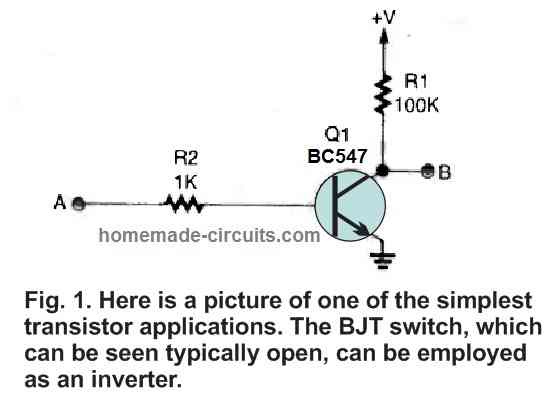

V tej objavi se bomo naučili, kako zgraditi logična vrata NOT, IN, NAND, OR in NOR z uporabo diskretnih tranzistorjev. Glavna prednost uporabe tranzistorskih logičnih vrat je, da lahko delujejo tudi pri napetostih tako nizkih kot 1,5 V.

V nekaterih elektronskih aplikacijah je lahko razpoložljiva napetost neustrezna za napajanje TTL ali celo CMOS IC. To še posebej velja za pripomočke, ki delujejo na baterije. Brez dvoma imate vedno na voljo možnost 3-voltnega logičnega IC. Vendar ti niso vedno lahko dostopni navdušencem ali eksperimentatorjem in ne delujejo pod svojimi določenimi specifikacijami napetosti (na splošno pod 2,5 volta DC).

Poleg tega je morda v aplikaciji, ki se napaja iz baterij, prostor samo za eno 1,5-voltno baterijo. No, kaj boš potem naredil? Običajno IC logična vrata bi lahko nadomestili s tranzistoriziranimi logičnimi vrati. Za vsaka določena logična vrata je na splošno potrebnih samo nekaj tranzistorjev, za tipično logiko pretvornika NOT vrat pa je potreben samo en tranzistor.

FET proti bipolarnemu tranzistorju

Tranzistorji z učinkom polja (FET) vs bipolarni tranzistorji : katera je boljša možnost za nizkonapetostna logična vezja? Ena odlična lastnost DEJSTVA je, da je njihov 'vklopni' upor neverjetno nizek. Poleg tega potrebujejo zelo nizek vklopni tok.

Vendar pa imajo eno omejitev pri izjemno nizkonapetostnih aplikacijah. Običajno je omejitev napetosti na vratih približno en volt. Poleg tega se lahko razpoložljiva napetost zmanjša pod optimalno delovno območje FET, če je na vrata pritrjen upor za omejevanje toka ali upor navzdol.

Nasprotno pa imajo bipolarni preklopni tranzistorji prednost pri aplikacijah z eno baterijo pri izjemno nizki napetosti, saj za vklop potrebujejo le 0,6 do 0,7 voltov.

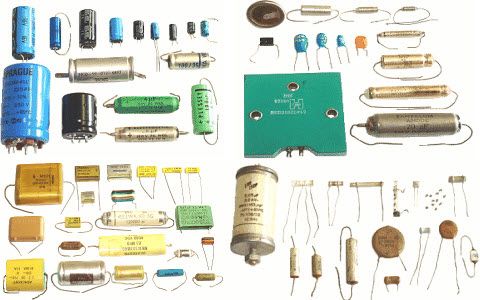

Poleg tega je večina običajnih FET-jev, ki se običajno prodajajo v embalaži z mehurčki v vaši najbližji trgovini z elektroniko, pogosto dražja od bipolarnih tranzistorjev. Poleg tega je na splošno mogoče kupiti velik paket bipolarnih tranzistorjev za ceno para FET-jev.

Ravnanje s FET zahteva bistveno več pozornosti kot ravnanje z bipolarnimi tranzistorji. Zaradi elektrostatične in splošne eksperimentalne zlorabe so FET-ji še posebej izpostavljeni poškodbam. Zgorele komponente lahko pokvarijo prijeten, ustvarjalen večer eksperimentiranja ali inovacij, da ne pozabimo na čustveno bolečino odpravljanja napak.

Osnove preklopnih tranzistorjev

Primeri logičnih vezij, razloženi v tem članku, uporabljajo bipolarne tranzistorje NPN, saj so cenovno dostopni in ne potrebujejo posebnega ravnanja. Da bi se izognili poškodbam naprave ali delov, ki jo podpirajo, je treba pred priključitvijo vezja izvesti ustrezne varnostne ukrepe.

Čeprav so naša vezja pretežno osredotočena na bipolarne spojne tranzistorje (BJT), bi jih lahko prav tako dobro sestavili s tehnologijo FET.

Osnovno stikalno vezje je preprosta tranzistorska aplikacija, ki je ena najlažjih zasnov.

Izdelava vrat NOT z enim tranzistorjem

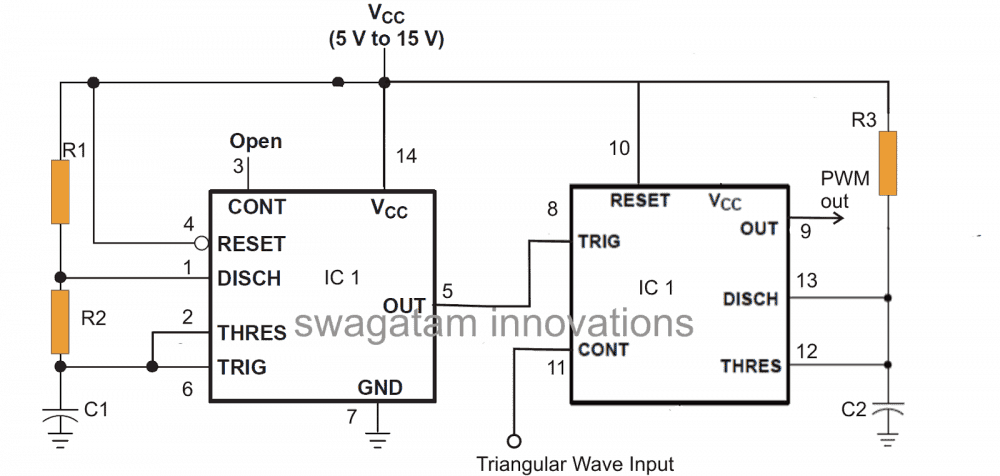

Shema tranzistorskega stikala je prikazana na sliki 1. Odvisno od tega, kako je implementirano v določeni aplikaciji, lahko stikalo ostane nizko ali normalno odprto.

Enostavna logična vrata NOT pretvornika se lahko ustvarijo z neposrednim preklopnim vezjem, prikazanim na sliki 1 (kjer je točka A vhod). Vrata NOT delujejo tako, da če na bazo tranzistorja (točka A; Q1) ni zagotovljena enosmerna prednapetost, ostanejo zaprta, kar ima za posledico visoko ali logično 1 (enako ravni V+) na izhodu ( točka B).

Vendar pa se tranzistor aktivira, ko je za bazo Q1 zagotovljena pravilna prednapetost, s čimer se izhod vezja potisne nizko ali na logično 0 (skoraj enako ničelnemu potencialu). Tranzistor z oznako Q1 je bipolarni tranzistor za splošno uporabo ali BC547, ki se običajno uporablja v stikalnih in ojačevalnih aplikacijah z nizko porabo.

Vsak tranzistor, ki mu je enakovreden (na primer 2N2222, 2N4401 itd.), bi deloval. Vrednosti R1 in R2 so bile izbrane tako, da so dosegle kompromis med nizkim tokom in združljivostjo. V vseh izvedbah so vsi upori 1/4 vata, 5 % enote.

Napajalna napetost je nastavljiva med 1,4 in 6 V DC. Upoštevajte, da lahko vezje deluje kot medpomnilnik, ko sta obremenitveni upor in izhodna povezava premaknjena na oddajnik tranzistorja.

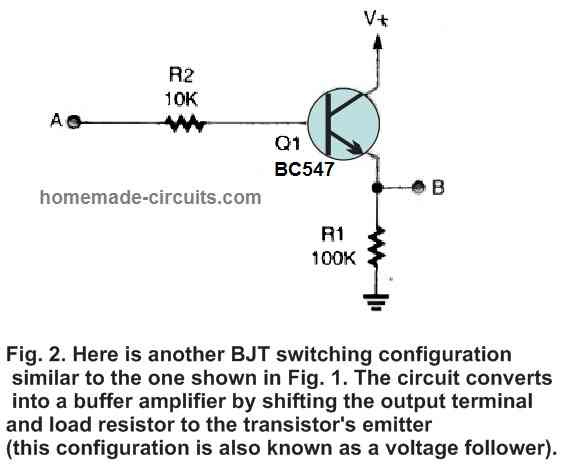

Izdelava vmesnih vrat z uporabo enega samega BJT BC547

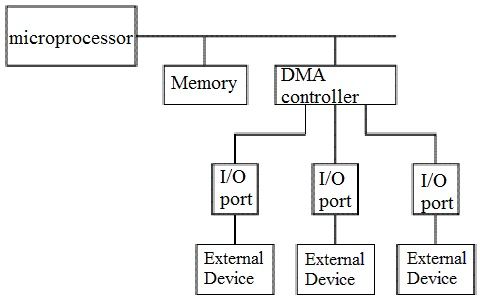

Sledilnik napetosti ali ojačevalnik vmesnega pomnilnika je vrsta logične preklopne konfiguracije, ki je enaka tisti, ki je prikazana na sliki 2. Upoštevati je treba, da sta bila obremenitveni upor in izhodni priključek premaknjena od zbiralnika tranzistorja do njegovega oddajnika v tem vezju, kar je glavna razlika med to zasnovo in tisto, prikazano na sliki 1.

Delovanje tranzistorja je mogoče 'obrniti' tudi s premikanjem bremenskega upora in izhodnega priključka na drugi konec BJT.

Z drugimi besedami, ko na vhod vezja ni pristranskosti, ostane izhod vezja nizek; ko pa se na vhod vezja dovede prednapetost ustrezne napetosti, postane izhod vezja visok. (To je ravno nasprotno od tega, kar se zgodi v prejšnjem krogu.)

Oblikovanje dvovhodnih logičnih vrat z uporabo tranzistorjev

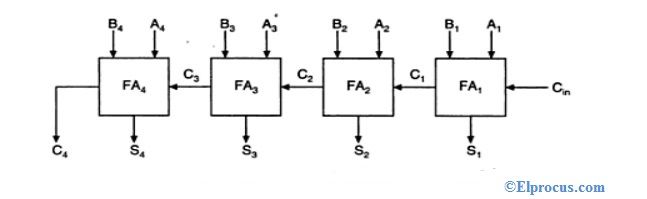

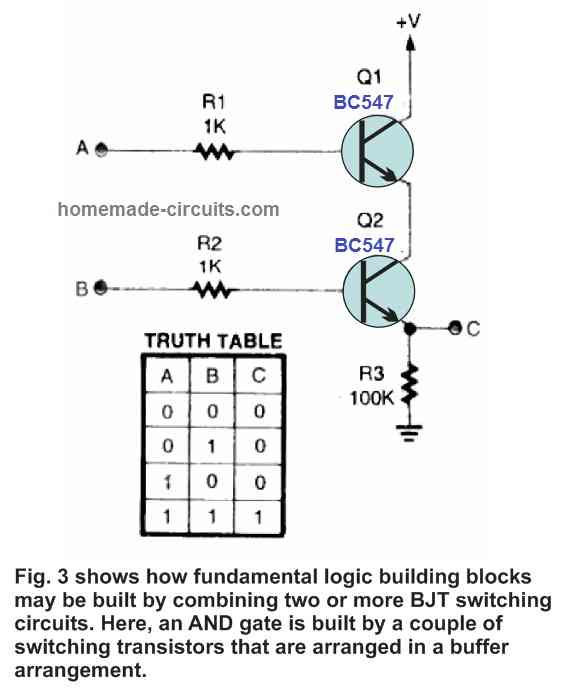

IN vrata z uporabo dveh tranzistorjev

Slika 3 prikazuje, kako je mogoče ustvariti osnovna vrata IN z dvema vhodoma z uporabo para medpomnilnikov, skupaj s tabelo resnic za ta vrata. Tabela resnic ponazarja, kakšni bi bili izhodni rezultati za vsak ločen niz vhodov. Točki A in B se uporabljata kot vhoda vezja, točka C pa služi kot izhod vezja.

Iz tabele resnic je pomembno poudariti, da samo en niz vhodnih parametrov povzroči logično nizek izhodni signal, medtem ko vse druge vhodne kombinacije povzročijo logično nizek izhod. Izhod vrat IN na sliki 3 ostane rahlo pod V+, ko postane visok.

To se zgodi zaradi padca napetosti med dvema tranzistorjema (Q1 in Q2).

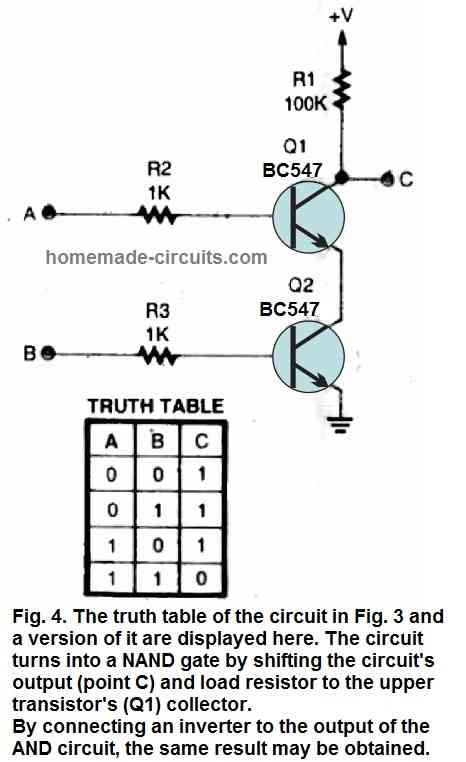

Vrata NAND z uporabo dveh tranzistorjev

Druga različica vezja na sliki 3 in pripadajoča tabela resnic sta prikazani na sliki 4. Vezje se spremeni v vrata NAND s premikom izhoda (točka C) in izhodnega upora na kolektor zgornjega tranzistorja (Q1).

Ker morata biti tako Q1 kot Q2 vklopljena, da povlečete nizko stran R1 na maso, je izguba napetosti na izhodu C nepomembna.

Če vrata tranzistorja AND ali tranzistorja NAND potrebujejo več kot dva vhoda, bi lahko v prikazane modele priključili več tranzistorjev, da bi zagotovili tri, štiri itd. vrata AND ali NAND.

Da bi nadomestili napetostne izgube posameznih tranzistorjev, je treba V+ ustrezno povečati.

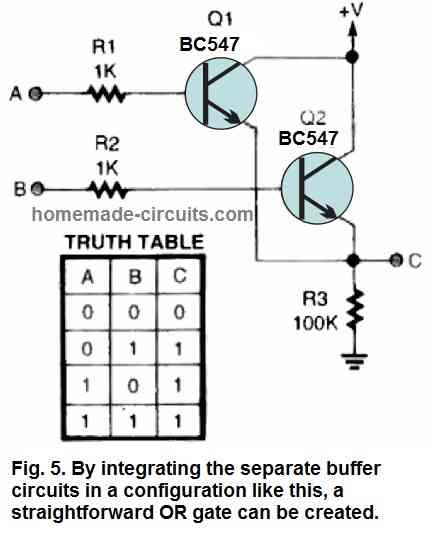

ALI vrata z uporabo dveh tranzistorjev

Druga oblika logičnega vezja z dvema vhodoma je prikazana na sliki 5, skupaj s tabelo resnic vezja ALI vrat.

Izhod vezja je visok, ko je vhod A ali B potisnjen visoko, vendar je zaradi kaskadnih tranzistorjev padec napetosti večji od 0,5 volta. Še enkrat, prikazane številke kažejo, da je dovolj napetosti in toka za delovanje naslednjih tranzistorskih vrat.

NOR vrata z uporabo dveh tranzistorjev

Slika 6 prikazuje naslednja vrata na našem seznamu, vrata NOR z dvema vhodoma, skupaj z njihovo tabelo resnic. Podobno kot se vrata IN in NAND odzivajo druga na drugo, tudi vezji ALI in NI delujeta enako.

Vsaka od prikazanih vrat je sposobna zagotoviti dovolj pogona za aktiviranje vsaj enega ali več sosednjih tranzistorskih vrat.

Aplikacije tranzistorskih logičnih vrat

Kaj počnete z zgoraj razloženimi digitalnimi vezji, ki jih zdaj imate? Vse, kar bi lahko dosegli z običajnimi vrati TTL ali CMOS, vendar brez skrbi glede omejitev napajalne napetosti. Tukaj je nekaj aplikacij tranzistorsko-logičnih vrat v akciji.

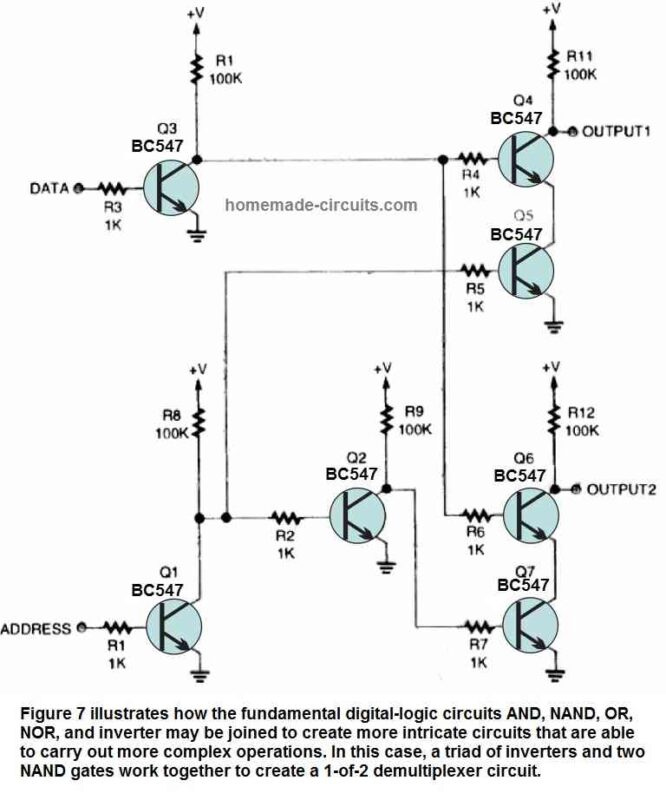

Demultipleksersko vezje

Na sliki 7 je prikazan demultiplekser 1-od-2 s tremi vrati NOT in dvema vezjema NAND. Ustrezen izhod je izbran z uporabo enobitnega 'naslovnega vnosa', ki je lahko OUTPUT1 ali OUTPUT2, medtem ko se uporabljajo informacije o vožnji. v vezje z uporabo vhoda DATA.

Vezje deluje najučinkoviteje, ko se hitrost prenosa podatkov vzdržuje pod 10 kHz. Funkcionalnost vezja je enostavna. Vhod PODATKOV se napaja z zahtevanim signalom, ki vklopi Q3 in obrne vhodne podatke na zbiralniku Q3.

Izhod Q1 je nastavljen na visoko raven, če je vhod ADDRESS nizek (ozemljen ali ni signala). Pri zbiralniku Q1 je visoka moč razdeljena na dve poti. Na prvi poti se izhod Q1 napaja na bazo Q5 (eden od krakov vrat NAND z dvema vhodoma), ki ga vklopi in s tem 'aktivira' vrata NAND, sestavljena iz Q4 in Q5.

Na drugi poti se visoki izhod Q1 istočasno dovaja na vhod drugih vrat NOT (Q2). Po dvojni inverziji se proizvodnja Q2 zmanjša. Ta nizek napaja bazo Q7 (en terminal drugih vrat NAND, sestavljen iz Q6 in Q7), s čimer se izklopi vezje NAND.

Vsaka informacija ali signal, uporabljen na vhodu DATA, v teh okoliščinah prispe na OUTPUT1. Druga možnost je, da je situacija obrnjena, če je visok signal na vhodu ADDRESS. To pomeni, da bodo vse informacije, posredovane vezju, prikazane na OUTPUT2, ker so vrata NAND Q4/Q5 onemogočena in vrata NAND Q6/Q7 omogočena.

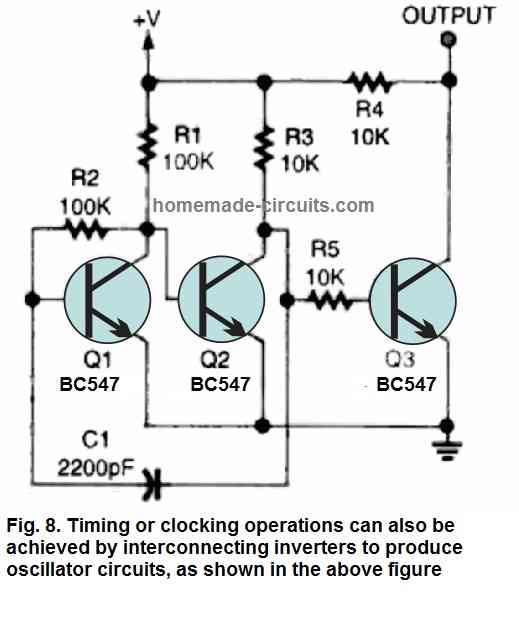

Oscilatorsko vezje (taktni generator)

Naša naslednja aplikacija tranzistorskih logičnih vrat, prikazana na sliki 8, je osnovni taktni generator (znan tudi kot oscilator), sestavljen iz treh običajnih pretvornikov NOT vrat (od katerih je eden pristranski z uporabo povratnega upora, R2, ki ga postavi v analogna regija).

Za izravnavo izhoda so vključena tretja vrata NOT (Q3), ki zagotavljajo komplement izhodu oscilatorja. Vrednost C1 se lahko poveča ali zmanjša, da se spremeni delovna frekvenca vezja. Izhodna valovna oblika ima frekvenco okoli 7 kHz z V+ pri 1,5 V DC, z uporabo navedenih vrednosti komponent.

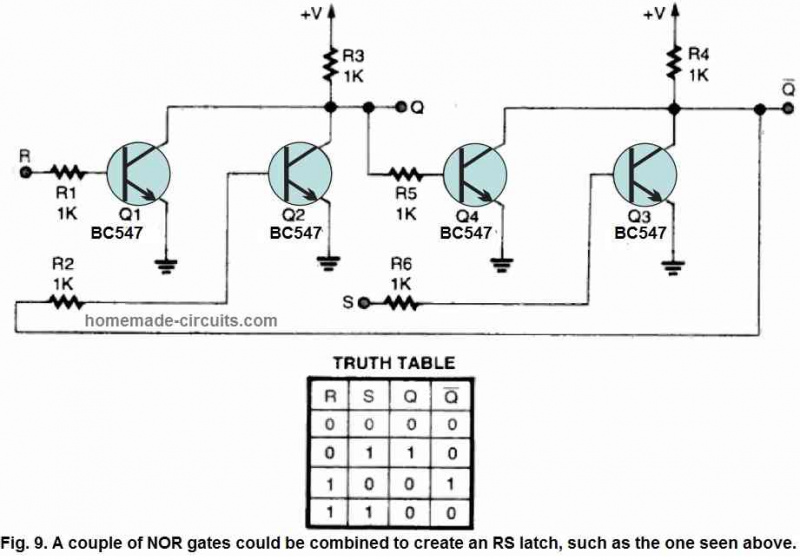

Krog zaklepa RS

Slika 9 prikazuje naše končno aplikacijsko vezje, zapah RS, sestavljen iz dveh vrat NOR. Da bi zagotovili zdrav izhodni pogon na izhodih Q in Q, sta upora R3 in R4 nastavljena na 1 k ohmov.

Resnična tabela zapaha RS je prikazana poleg shematskega načrta. To je le nekaj ilustracij več zanesljivih, nizkonapetostnih, digitalnih vezij z logičnimi vrati, ki jih je mogoče ustvariti z uporabo posameznih tranzistorjev.

Vezja, ki uporabljajo tranzistorizirano logiko, potrebujejo preveč delov

Veliko težav je mogoče rešiti z uporabo vseh teh nizkonapetostnih tranzistorskih logičnih vezij. Vendar pa bi uporaba preveč teh tranzistoriziranih vrat lahko povzročila nove težave.

Število tranzistorjev in uporov lahko postane dokaj veliko, če aplikacija, ki jo gradite, vsebuje veliko število vrat, ki zasedajo dragocen prostor.

Uporaba nizov tranzistorjev (veliko tranzistorjev, obdanih s plastiko) in uporov SIP (Single Inline Package) namesto posameznih enot je eden od načinov za rešitev tega problema.

Zgornji pristop lahko prihrani tono prostora na tiskanem vezju, hkrati pa ohrani zmogljivost, ki je enaka zmogljivosti njihovih ekvivalentov polne velikosti. Nizi tranzistorjev so na voljo v embalaži za površinsko montažo, 14-nožnimi skoznjimi luknjami in štirikratnem pakiranju.

Za večino vezij so mešalni tipi tranzistorjev povsem sprejemljivi.

Kljub temu je priporočljivo, da eksperimentator dela z eno samo vrsto tranzistorja za gradnjo tranzistoriziranih logičnih vezij (kar pomeni, da če ustvarite del vrat z uporabo BC547, nato poskusite uporabiti isti BJT tudi za izdelavo drugih preostalih vrat).

Razlog je v tem, da imajo lahko različne različice tranzistorjev nekoliko različne lastnosti in se zato lahko obnašajo drugače.

Na primer, za nek tranzistor je lahko meja osnovnega vklopa večja ali manjša od druge ali pa ima lahko skupni tokovni dobiček, ki je nekoliko višji ali nižji.

Po drugi strani pa bi lahko bili nižji tudi stroški nakupa velike škatle ene same vrste tranzistorja. Učinkovitost vaših vezij se bo izboljšala, če so vaša logična vrata zgrajena z uporabo ujemajočih se tranzistorjev, projekt v celoti pa bo na koncu bolj nagrajen.