Ta članek pojasnjuje generiranje impulzne širinske modulacije signali s spremenljivim delovnim ciklom na FPGA z uporabo VHDL. PWM ima fiksno frekvenco in spremenljivo napetost. V tem članku je obravnavan tudi Digital Clock Manager za zmanjšanje frekvence ure z zmanjšanjem naklona signala ure. Fiksna frekvenca se uporablja za izdelavo vhodnih podatkov, ki s primerjalnikom proizvajajo signale PWM. Elektronska podjetja s svojimi standardi in protokoli oblikujejo strojno opremo, namenjeno njihovim izdelkom, zato je za končne uporabnike izziv, da ponovno konfigurirajo strojno opremo glede na njihove potrebe. Ta zahteva po strojni opremi je privedla do rasti novega segmenta, ki ga je mogoče prilagoditi strankam poljsko programibilna integrirana vezja, imenovana FPGA .

Modulacija impulzne širine (PWM)

Modulacija širine impulza se pogosto uporablja v komunikacijskih aplikacijah in nadzorni sistemi . Modulacijo širine impulza lahko generiramo z različnimi pristopi v nadzornih sistemih. V tem članku je PWM ustvarjen z uporabo jezika za opis strojne opreme (VHDL) in implementiran na FPGA. Izvedba PWM na FPGA lahko hitreje obdela podatke in arhitekturo krmilnika lahko optimizira glede na prostor ali hitrost.

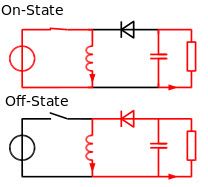

PWM je tehnika za zagotavljanje logike '0' in logike '1' za nadzorovano časovno obdobje. Je vir signala, ki vključuje modulacijo njegovega delovnega cikla za nadzor količine moči, poslane v obremenitev. V PWM se časovno obdobje kvadratnega vala ohranja konstantno in čas, za katerega signal ostane VISOK, se spreminja.

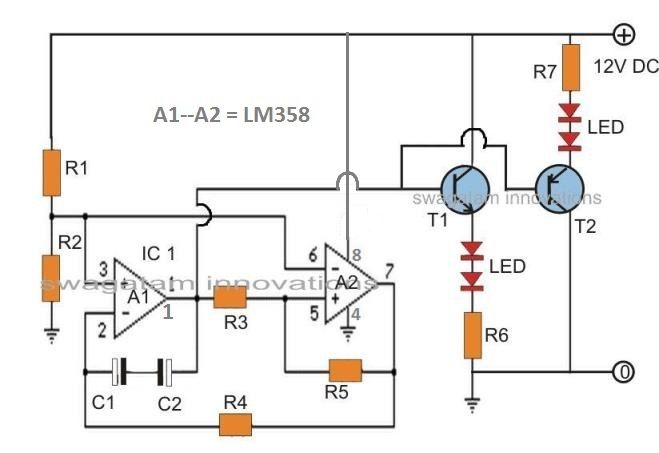

PWM generira impulze na svojem izhodu tako, da je povprečna vrednost HIGHs in LOWs sorazmerna vhodu PWM. Delovni cikel signala je lahko različen. PWM signal je kvadratni val konstantnega obdobja z različnim delovnim ciklom. To pomeni, da je frekvenca signala PWM konstantna, vendar ostaja časovno obdobje signala visoko in se spreminja, kot je prikazano.

Signal PWM

VHDL

VHDL je jezik, ki se uporablja za opis vedenja zasnove digitalnih vezij . VHDL uporabljajo industrije in akademiki za simulacijo digitalnih vezij. Njeno zasnovo je mogoče simulirati in prevesti v obliki, ki je primerna za vgradnjo v strojno opremo.

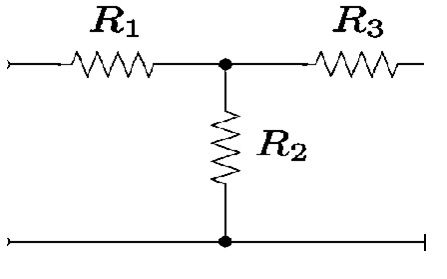

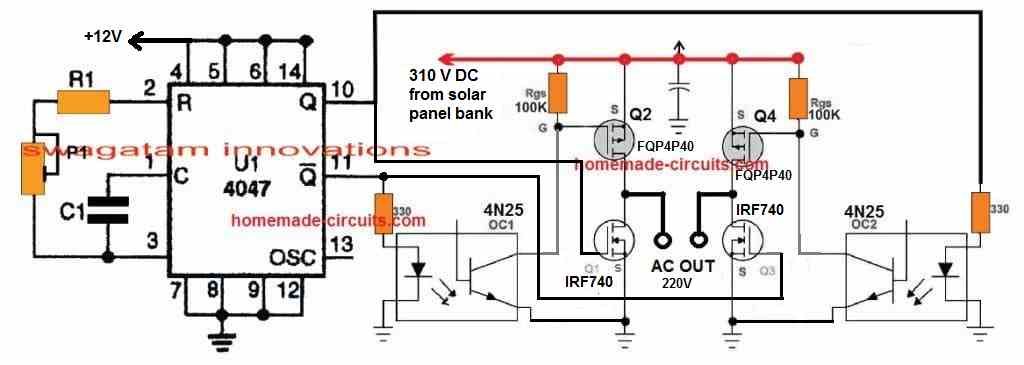

PWM arhitektura

Za izdelavo vhodnih podatkov za generiranje PWM uporabljamo hitri N-bitni prosti števec, katerega izhod se primerja z izhodom registra in s pomočjo primerjalnika shrani želeni vhodni delovni cikel. Primerjava izhod je nastavljen na 1, če sta obe vrednosti enaki. Ta primerjalni izhod se uporablja za nastavitev zapaha RS. Signal prelivanja s števca se uporablja za ponastavitev zapaha RS. The izhod zapaha RS daje želeni izhod PWM. Ta signal prelivanja se uporablja tudi za nalaganje novega N-bitnega delovnega cikla v register. PWM ima fiksno frekvenco in spremenljivo napetost. Ta vrednost napetosti se spremeni od 0V do 5 V.

PWM signal s spremenljivim delovnim ciklom

Osnovni PWM generira signale, ki daje izhod PWM, zahteva primerjalnik, ki primerja dve vrednosti. Prva vrednost predstavlja kvadratni signal, ki ga generira N bitni števec, druga vrednost pa kvadratni signal, ki vsebuje informacije o delovnem ciklu. Števec ustvari signal obremenitve vsakič, ko pride do prelivanja. Ko signal obremenitve postane aktiven, register naloži novo vrednost delovnega cikla. Signal obremenitve se uporablja tudi za ponastavitev zapaha. Izhod zapaha je signal PWM. To se spreminja s spremembo vrednosti delovnega cikla.

Kaj je FPGA?

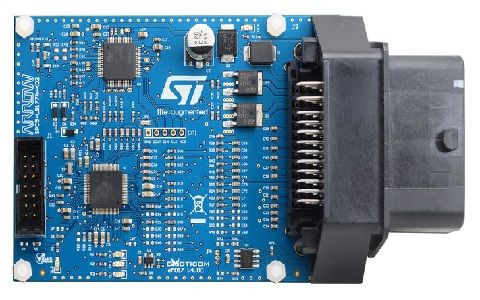

FPGA je poljsko programabilna matrika vrat. To je vrsta naprave, ki se pogosto uporablja v elektronskih vezjih. FPGA so polprevodniške naprave ki vsebujejo programabilne logične bloke in medsebojna vezja. Po izdelavi ga je mogoče programirati ali ponovno programirati na zahtevano funkcionalnost.

FPGA

Osnove FPGA

Ko je izdelano vezje in če kot del vsebuje FPGA. To se programira med proizvodnim procesom in ga lahko pozneje znova programirate, da ustvarite posodobitev ali naredite potrebne spremembe. Zaradi te lastnosti FPGA je ASIC edinstven. Integrirana vezja (ASIC), specifična za uporabo, so izdelana po meri za določeno projektno nalogo. V preteklosti se FPGA uporabljajo za razvoj nizke hitrosti, zapletenosti in oblikovanja glasnosti, danes pa bo FPGA zlahka premaknil mejo zmogljivosti do 500 MHz.

V mikrokrmilnikih je čip zasnovan za stranko, ki mora napisati programsko opremo in jo sestaviti v šestnajstiško datoteko, da se naloži na mikrokrmilnik. To programsko opremo je mogoče enostavno zamenjati, ker je shranjena v pomnilniku Flash. V FPGA ni procesorja, ki bi poganjal programsko opremo, mi pa smo tisti, ki načrtujemo vezje. FPGA lahko konfiguriramo tako preprosto kot vrata AND ali kompleksno kot večjedrni procesor. Za oblikovanje modela napišemo Hardware Description Language (HDL), ki je dveh vrst - Verilog in VHDL. Nato se HDL sintetizira v bitno datoteko z uporabo BITGEN za konfiguracijo FPGA. FPGA shrani konfiguracijo v RAM, to pomeni, da se konfiguracija izgubi, ko ni povezave z električno energijo. Zato jih je treba konfigurirati vsakič, ko se napaja.

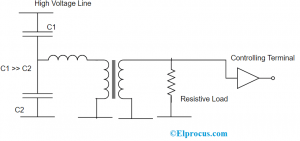

Arhitektura FPGA

FPGA so montažni silicijevi čipi, ki jih je mogoče električno programirati za izvajanje digitalnih modelov. Prvi FPGA na osnovi statičnega pomnilnika, imenovan SRAM, se uporablja za konfiguriranje logike in medsebojne povezave s pomočjo toka konfiguracijskih bitov. Današnji sodobni EPGA vsebuje približno 3.30.000 logičnih blokov in približno 1.100 vhodov in izhodov.

Arhitektura FPGA

Arhitektura FPGA je sestavljena iz treh glavnih komponent

- Programabilni logični bloki, ki izvajajo logične funkcije

- Programabilno usmerjanje (medsebojne povezave), ki izvaja funkcije

- V / I bloki, ki se uporabljajo za vzpostavitev povezav brez čipa

Uporaba PWM signalov

PWM signali se pogosto uporabljajo za nadzorne aplikacije. Tako kot krmiljenje enosmernih motorjev, regulacijskih ventilov, črpalk, hidravlike itd. Tu je nekaj aplikacij signalov PWM.

- Ogrevalni sistemi s počasnimi časi od 10 do 100 Hz ali več.

- Enosmerni elektromotorji 5 do 10KHz

- Napajalniki ali ojačevalniki zvoka 20 do 200 KHz.

Ta članek govori o generiranje PWM signalov s spremenljivim delovnim ciklom z uporabo FPGA. Poleg tega se lahko za kakršno koli pomoč pri elektronskih projektih ali dvome v zvezi s tem člankom obrnete na nas tako, da komentirate spodnji odsek za komentarje.