Tranzistor MOS je najbolj temeljni element v velikem načrtovanju integriranih vezij. Ti tranzistorji so na splošno razvrščeni v dve vrsti PMOS in NMOS. Kombinacija tranzistorjev NMOS in PMOS je znana kot a CMOS tranzistor . Drugačen logična vrata & druge digitalne logične naprave, ki se izvajajo, morajo imeti logiko PMOS. Ta tehnologija je poceni in ima dobro odpornost na motnje. Ta članek obravnava eno od vrst tranzistorjev MOS, kot je tranzistor PMOS.

Kaj je tranzistor PMOS?

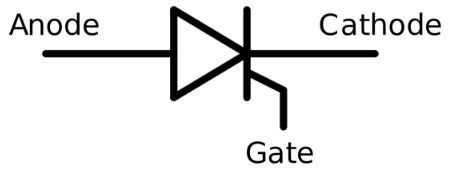

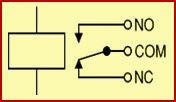

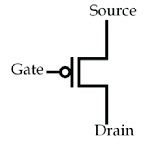

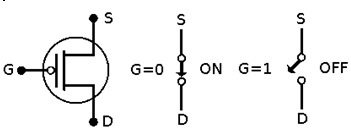

PMOS tranzistor ali P-kanalni polprevodnik kovinskega oksida je nekakšen tranzistor, kjer se v območju kanala ali vrat uporabljajo dopanti tipa p. Ta tranzistor je ravno nasprotje tranzistorja NMOS. Ti tranzistorji imajo tri glavne terminale; izvor, vrata in odtok, kjer je izvor tranzistorja zasnovan s substratom tipa p, odvodni terminal pa je zasnovan s substratom tipa n. V tem tranzistorju so nosilci naboja, kot so luknje, odgovorni za prevajanje toka. Spodaj so prikazani simboli tranzistorjev PMOS.

Kako deluje PMOS tranzistor?

Delovanje tranzistorja tipa p je povsem nasprotno od tranzistorja tipa n. Ta tranzistor bo tvoril odprto vezje, kadarkoli dobi nezanemarljivo napetost, kar pomeni, da ni pretoka električne energije od terminala vrat (G) do vira (S). Podobno ta tranzistor tvori zaprto vezje, ko dobi napetost okoli 0 voltov, kar pomeni, da tok teče od priključka vrat (G) do odtoka (D).

Ta mehurček je znan tudi kot inverzijski mehurček. Glavna funkcija tega kroga je torej obračanje vrednosti vhodne napetosti. Če priključek vrat zagotavlja napetost 1, jo bo ta pretvornik spremenil v nič in ustrezno deloval vezje. Torej je funkcija tranzistorja PMOS in tranzistorja NMOS precej nasprotna. Ko jih združimo v eno samo vezje MOS, bo to postalo vezje CMOS (komplementarni kovinsko-oksidni polprevodnik).

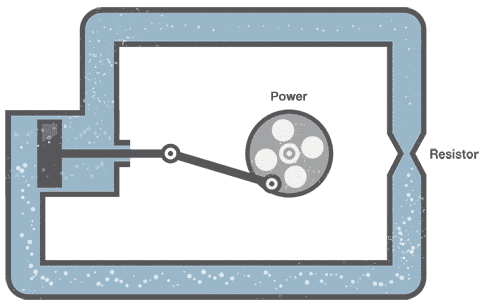

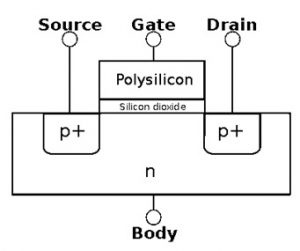

Prerez tranzistorja PMOS

Spodaj je prikazan prerez PMOS tranzistorja. Tranzistor pMOS je zgrajen s telesom tipa n, ki vključuje dve polprevodniški področji tipa p, ki mejita na vrata. Ta tranzistor ima krmilna vrata, kot je prikazano na diagramu, ki nadzoruje pretok elektronov med obema priključkoma, kot sta vir in odtok. V tranzistorju pMOS je telo pri +ve napetosti. Ko je priključek vrat pozitiven, sta priključka izvora in odvoda obratno prednapeta. Ko se to zgodi, toka ni več, zato bo tranzistor IZKLOPLJEN.

Ko se napetost na priključku vrat zniža, bodo nosilci pozitivnega naboja privlečeni na dno vmesnika Si-SiO2. Kadarkoli napetost pade dovolj nizko, se kanal obrne in ustvari prevodno pot od izvornega terminala do odtoka, tako da omogoči pretok toka.

Kadarkoli se ti tranzistorji ukvarjajo z digitalno logiko, imajo običajno dve različni vrednosti, kot sta 1 in 0 (ON in OFF). Pozitivna napetost tranzistorja je znana kot VDD, ki predstavlja logično visoko (1) vrednost v digitalnih vezjih. Nivo napetosti VDD v TTL logika na splošno okoli 5V. Trenutno tranzistorji dejansko ne morejo vzdržati tako visokih napetosti, ker se običajno gibljejo od 1,5 V do 3,3 V. Nizka napetost je pogosto znana kot GND ali VSS. Torej VSS pomeni logično '0' in je tudi običajno nastavljen na 0V.

Tranzistorsko vezje PMOS

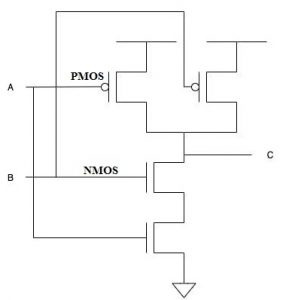

Zasnova vrat NAND z uporabo tranzistorja PMOS in tranzistorja NMOS je prikazana spodaj. Na splošno so vrata NAND v digitalni elektroniki logična vrata, ki se imenujejo tudi vrata NE-IN. Izhod teh vrat je nizek (0) le, če sta oba vhoda visoka (1) in je njegov izhod dopolnilo vratom IN. Če je kateri koli od obeh vhodov NIZEK (0), daje visoke izhodne rezultate.

Če je v spodnjem logičnem vezju vhod A 0 in B 0, bo vhod pMOS proizvedel '1', vhod nMOS pa '0'. Torej ta logična vrata ustvarijo logično '1', ker so povezana z virom prek zaprtega vezja in ločena od GND prek odprtega vezja.

Ko je A '0' in B' je '1', potem bo vhod pMOS ustvaril '1' in vhod NMOS bo ustvaril '0'. Tako bodo ta vrata proizvedla logično, ker so povezana z virom prek zaprtega vezja in ločena od GND z odprtim vezjem. Ko je A '1' in B '0', bo vhod 'B' pMOS ustvaril visok izhod (1) in 'B' vhod NMOS bo ustvaril nizek izhod (0). Torej bodo ta logična vrata ustvarila logično 1, ker so povezana z virom prek zaprtega vezja in ločena od GND z odprtim vezjem.

Ko je A '1' in B je '1', bo A vhod' pMOS ustvaril ničlo, A vnos nMOS pa bo ustvaril '1'. Posledično bi morali preveriti tudi vhod B pMOS in nMOS. Vhod B pMOS bo ustvaril '0' in vhod B nMOS bo ustvaril '1'. Torej bodo ta logična vrata ustvarila logično '0', ker so ločena od vira z odprtim krogom in povezana z GND prek zaprtega kroga.

Tabela resnice

Tabela resničnosti zgornjega logičnega vezja je podana spodaj.

|

A |

B |

C |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

Mejna napetost tranzistorja PMOS je običajno 'Vgs', ki je potrebna za ustvarjanje kanala, znanega kot inverzija kanala. V tranzistorju PMOS sta substrat in izvorni priključek preprosto priključena na 'Vdd'. Če začnemo zniževati napetost s sklicevanjem na izvorno sponko na vratni sponki od Vdd do točke, kjer opazite inverzijo kanala, na tem položaju, če analizirate Vgs in vir z visokim potencialom, potem boste dobili negativno vrednost. Torej ima tranzistor PMOS negativno vrednost Vth.

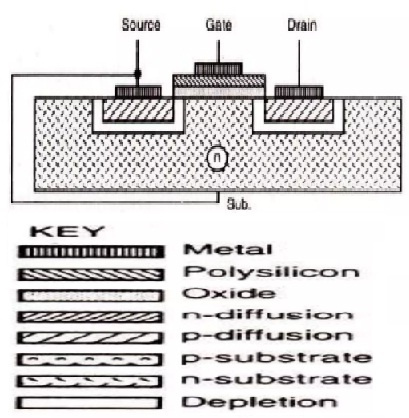

Postopek izdelave PMOS

Spodaj so opisani koraki pri izdelavi tranzistorja PMOS.

Korak 1:

Tanka plast silicijeve rezine se spremeni v material tipa N s preprostim dopiranjem fosforjevega materiala.

2. korak:

Debela plast silicijevega dioksida (Sio2) se goji na popolnem substratu p-tipa.

3. korak:

Zdaj je površina prevlečena s fotorezistom čez debelo plast silicijevega dioksida.

4. korak:

Nato se ta plast preprosto izpostavi UV-svetlobi skozi masko, ki definira področja, v katera naj bi potekala difuzija skupaj s tranzistorskimi kanali.

5. korak:

Ta območja so vrezana skupaj s silicijevim dioksidom, ki leži spodaj, tako da je površina rezine izpostavljena znotraj okna, ki ga določa maska.

6. korak:

Preostali fotorezist se loči in tanka plast Sio2 se naraste običajno 0,1 mikrometra po celotni površini čipa. Nato se čez to namesti polisilicij, da tvori strukturo vrat. Fotorezist je nameščen čez celotno plast polisilicija in izpostavlja UV svetlobo skozi masko2.

7. korak:

Difuzije se dosežejo s segrevanjem rezin na najvišjo temperaturo in prehajanjem plina z želenimi nečistočami p-tipa, kot je bor.

8. korak:

Goji se silicijev dioksid debeline 1 mikrometra in nanj se nanese fotorezist. Izpostavite ultravijolično svetlobo z masko3 na želenih območjih vrat, vira in odtoka, ki so vgravirani, da naredijo kontaktne reze.

9. korak:

Zdaj se kovina ali aluminij nanese na površino debeline 1 mikrometra. Spet se po vsej kovini naraste fotorezistni material in izpostavi UV svetlobi skozi masko4, ki je vgravirana, da se oblikuje zahtevana zasnova medsebojne povezave. Končna struktura PMOS je prikazana spodaj.

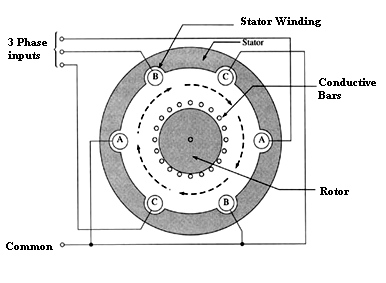

Značilnosti PMOS tranzistorja

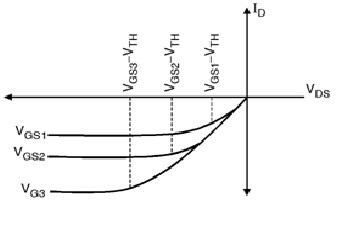

Spodaj so prikazane I-V karakteristike PMOS tranzistorja. Te značilnosti so razdeljene na dve regiji, da bi dobili razmerje med tokom odtoka in vira (I DS) ter njegovimi napetostmi na sponkah, kot sta linearna in nasičena območja.

V linijskem območju se bo IDS linearno povečal, ko se bo povečal VDS (napetost od odtoka do vira), medtem ko je v območju nasičenja I DS stabilen in neodvisen od VDS. Glavno razmerje med ISD (vir in odvodni tok) in njegovimi priključnimi napetostmi je izpeljano s podobnim postopkom tranzistorja NMOS. V tem primeru bodo edina sprememba nosilci naboja, ki so prisotni v inverzijski plasti, preprosto luknje. Ko se luknje premaknejo od vira do odtoka, je tudi tok enak.

Tako se v trenutni enačbi pojavi negativni predznak. Poleg tega so vse uporabljene prednapetosti na sponkah naprave negativne. Torej, značilnosti tranzistorja PMOS ID - VDS so prikazane spodaj.

Enačba odtočnega toka za tranzistor PMOS v linearnem območju je podana kot:

ID = – mp Cox

Podobno je enačba odvodnega toka za tranzistor PMOS v območju nasičenja podana kot:

ID = – mp Cox (VSG – | V TH |p )^2

Kjer je 'mp' mobilnost luknje & '|VTH| p’ je mejna napetost tranzistorja PMOS.

V zgornji enačbi negativni predznak pomeni, da ID ( odvodni tok ) teče od odtoka (D) do izvira (S), medtem ko luknje tečejo v nasprotni smeri. Ko je mobilnost luknje nizka v primerjavi z mobilnostjo elektronov, potem tranzistorji PMOS trpijo zaradi zmožnosti pogona z nizkim tokom.

To je torej vse o pregledu PMOS tranzistorja ali mos tranzistorja tipa p – izdelava, vezje in njegovo delovanje. PMOS tranzistorji so zasnovani s p-virom, n-substratom in odtokom. Nosilci naboja PMOS so luknje. Ta tranzistor vodi, ko je na priključku vrat uporabljena nizka napetost. Naprave, ki temeljijo na PMOS, so manj dovzetne za motnje v primerjavi z napravami NMOS. Ti tranzistorji se lahko uporabljajo kot napetostno krmiljeni upori, aktivna bremena, tokovna zrcala, trans-impedančni ojačevalniki, uporabljajo pa se tudi v stikalih in napetostnih ojačevalnikih. Tukaj je vprašanje za vas, kaj je NMOS tranzistor?