ECL (emitter sklopljena logika) je avgusta 1956 v IBM-u prvič izumil Hannon S. Yourke. Ta logika je znana tudi kot logika trenutnega načina, ki se uporablja v računalnikih IBM 7090 in 7094. Družina ECL je zelo hitra v primerjavi z digitalna logika družine. Na splošno ta logična družina zagotavlja zakasnitev širjenja manj kot 1 ns. To je logična družina, ki temelji na bipolarnih spojnih tranzistorjih. Je najhitrejše logično družinsko vezje, ki je dostopno za načrtovanje običajnega logičnega sistema. Ta članek obravnava pregled an oddajno sklopljeno logično vezje , delo z aplikacijami.

Kaj je Emitter Coupled Logic?

Emitersko sklopljena logika je najboljša BJT logična družina, ki se uporablja v konvencionalni zasnovi logičnega sistema. Včasih se imenuje tudi logika trenutnega načina, ki je zelo hitra digitalna tehnologija. Na splošno velja, da je ECL najhitrejši logični IC, kjer doseže svoje visokohitrostno delovanje z uporabo zelo majhnega nihanja napetosti in prepreči, da bi tranzistorji vstopili v območje nasičenosti.

Izvedba ECL uporablja pozitivno napajalno napetost, ki je znana kot PECL ali ECL s pozitivno referenco. V zgodnjih vratih ECL se zaradi odpornosti na hrup uporablja negativna napetost. Po tem je ECL s pozitivnimi referencami postal zelo znan zaradi bolj združljivih logičnih ravni v primerjavi z logičnimi družinami TTL.

Emitersko sklopljena logika razprši ogromno količino statične moči, vendar je njena skupna poraba toka majhna v primerjavi z CMOS pri visokih frekvencah. ECL je torej koristen predvsem v tokokrogih za distribucijo ure in visokofrekvenčnih aplikacijah.

Emitersko sklopljene logične funkcije

Zaradi lastnosti ECL se bodo uporabljali v številnih visokozmogljivih aplikacijah.

- ECL zagotavlja dva izhoda, ki se vedno dopolnjujeta, ker delovanje vezja temelji na diferencialnem ojačevalniku.

- Ta logična družina je primerna predvsem za monolitne metode izdelave, ker so logične ravni funkcija razmerij uporov.

- Naprave družine ECL ustvarijo pravi in komplementarni izhod predlagane funkcije brez uporabe zunanjih pretvornikov. Posledično zmanjša število paketov in zahteve po moči ter zmanjša težave, ki nastanejo zaradi časovnih zakasnitev.

- Naprave ECL v zasnovi diferencialnih ojačevalnikov ponujajo široko prilagodljivost delovanja, tako da vezja ECL omogočajo uporabo kot digitalna in linearna vezja.

- Zasnova vrat ECL ima običajno visoko in nizko vhodno impedanco, kar je izjemno ugodno za doseganje velikega razprševanja in zmogljivosti pogona.

- Naprave ECL ustvarjajo konstanten odvod toka v napajalniku, da poenostavijo zasnovo napajalnika.

- Naprave ECL, vključno z izhodi odprtega oddajnika, preprosto omogočajo vključitev pogonske zmogljivosti prenosnega voda.

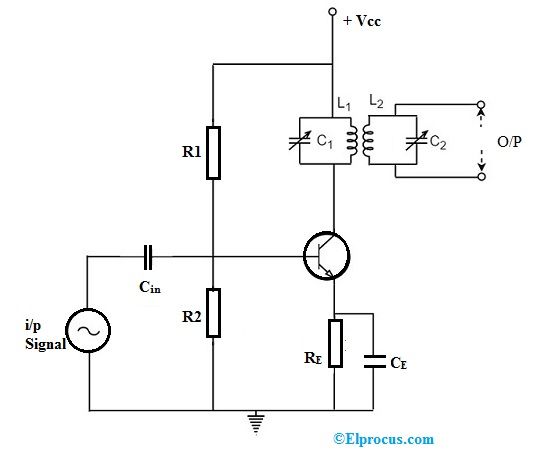

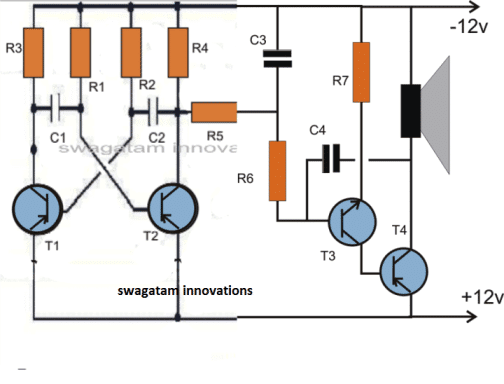

Emitersko sklopljeno logično vezje

Spodaj je prikazano z emiterjem sklopljeno logično vezje za pretvornik, ki je zasnovano z upori in tranzistorji. V tem vezju sta oddajna priključka dveh tranzistorjev preprosto povezana z uporom za omejevanje toka RE, ki se uporablja za preprečevanje vstopa tranzistorja v nasičenost. Tukaj je izhod tranzistorja vzet iz kolektorskega terminala namesto oddajnega terminala. To vezje zagotavlja dva izhoda Vout (invertirajoči izhod) in Vout2 (neinvertirajoči izhod) ter vhodni terminal, kot je Vin, kjer je podan visok ali nizek vhod. +Vcc = 5V.

Kako deluje oddajno sklopljena logika?

Delovanje emitersko sklopljene logike je, da kadar koli je v vezje ECL vhod HIGH, bo tranzistor 'Q1' VKLOPLJEN in tranzistor Q2 IZKLOPLJEN, vendar tranzistor Q1 ni nasičen. Tako bo to potegnilo izhod VOUT2 na VISOKO, vrednost izhoda VOUT1 pa bo NIZKA zaradi padca znotraj R1.

Podobno, ko je vrednost VIN, podana ECL, NIZKA, bo tranzistor Q1 izklopil in tranzistor Q2 VKLOPIL. Torej se tranzistor Q2 ne bo premaknil v nasičenost. Tako bo izhod VOUT1 povzročil VISOKO vrednost, izhodna vrednost VOUT2 pa bo nizka zaradi padca upora R2.

Oglejmo si, kako se tranzistorja Q1 in Q2 vklopita in izklopita, ko je priključena napetost.

Dva tranzistorja, kot sta Q1 in Q2 v tem vezju, sta povezana kot diferencialni ojačevalnik s skupnim oddajnim uporom.

Napajalna napetost za ta primer vezja je VCC = 5,0, VBB = 4,0 & VEE = 0 V. Vhodne vrednosti VISOKE in NIZKE ravni so preprosto definirane kot 4,4 V in 3,6 V. Pravzaprav to vezje ustvari NIZEK izhod in VISOKE ravni, ki so za 0,6 V višje; vendar se to popravi znotraj dejanskih krogov ECL.

Ko je Vin VISOK, je tranzistor Q1 vklopljen, vendar ni nasičen in tranzistor Q2 je izklopljen. Torej se izhodna napetost, kot je VOUT2, potegne na 5 V skozi upor R2 in lahko se pokaže, da je padec napetosti na uporu R1 približno 0,8 V, tako da je VOUT1 = 4,2 V (NIZEK). Poleg tega VE = VOUT1 – VQ1 => 4,2 V – 0,4 V = 3,8 V, ko je tranzistor Q1 popolnoma vklopljen.

Ko je Vin NIZEK, bo tranzistor Q2 vklopljen, vendar ne nasičen in tranzistor Q1 je IZKLOPLJEN. Zato se VOUT1 potegne na 5,0 V z uporabo upora R1 in lahko se pokaže, da je VOUT2 4,2 V. Tudi VE => VOUT2 – VQ2 => 4,2 V – 0,8 V => 3,4 V, ko je tranzistor Q2 vklopljen.

Pri ECL dva tranzistorja nikoli nista v nasičenosti kot t Nihanja vhodne/izhodne napetosti so dokaj majhna, kot je 0,8 V in vhodna impedanca je visoka, izhodni upor pa nizek. To pomaga ECL, da deluje hitreje z manj časa zakasnitve širjenja.

Krog z dvema vhodoma, povezanim oddajnikom ALI/NE

Spodaj je prikazano vezje logičnih vrat ALI/NE z dvema vhodnima oddajnikoma. To vezje je zasnovano s spremembo zgornjega inverterskega vezja. Sprememba je z dodajanjem dodatnega tranzistorja na vhodni strani.

Delovanje tega vezja je zelo preprosto. Ko so vhodi na obeh tranzistorjih Q1 in Q2 nizki, bo izhod1 (Vout1) nastavljen na VISOKO vrednost. Torej ta Vout1 ustreza izhodu vrat NOR.

Istočasno, če je tranzistor Q3 vklopljen, bo drugi izhod (Vout2) postal HIGH. Torej ta izhod Vou2 ustreza izhodu vrat ALI.

Na enak način, če sta oba vhoda tranzistorjev Q1 in Q2 VISOKA, bo vklopil tranzistorja Q1 in Q2 in zagotovil nizek izhod na terminalu VOUT1.

Če je tranzistor Q3 med to operacijo IZKLOPLJEN, bo zagotovil visok izhod na priključku VOUT2. Tabela resnic za vrata ALI/NI je torej podana spodaj.

|

Vložki |

Vložki | ALI |

NE |

|

A |

B | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Emitersko sklopljene logične značilnosti

Značilnosti ECL vključujejo naslednje.

- V primerjavi s TTL ima ECL hitrejši čas širjenja v razponu od 0,5 do 2 ns. Toda disipacija moči, povezane z oddajnikom, je višja v primerjavi s TTL, kot je 30 mW.

- V/I napetosti ECL imajo majhen nihaj, kot je 0,8.

- Vhodna impedanca ECL je visoka in izhodni upor nizek; posledično tranzistor zelo hitro spreminja svoja stanja.

- Zmogljivost ventilatorjev ECL je visoka in zakasnitve vrat so nizke.

- O/p logika ECL se spremeni iz stanja LOW v stanje HIGH, vendar se ravni napetosti za ta stanja razlikujejo med TTL in EC.

- Odpornost proti hrupu ECL je 0,4 V.

Prednosti in slabosti

The prednosti emitersko sklopljene logike so obravnavani spodaj.

- Ventilator ECL je 25, kar je bolje v primerjavi s TTL in nizko v primerjavi s CMOS.

- Povprečni čas zakasnitve širjenja ECL je 1 do 4 ns, kar je boljše v primerjavi s CMOS in

- TTL. Zato se imenuje najhitrejša logična družina.

- Ko sta BJT v oddajniku povezana logična vrata delujejo v aktivni regiji, potem imajo največjo hitrost v primerjavi z vsemi logičnimi družinami.

- Vrata ECL ustvarjajo komplementarne izhode.

- V napajalnih vodih ni tokovnih preklopnih konic.

- Izhode je mogoče povezati skupaj, da zagotovite funkcijo žično ALI.

- Parametri ECL se s temperaturo ne spreminjajo veliko.

- Št. Funkcij, ki so dostopne iz enega samega čipa, je veliko.

The slabosti emitersko sklopljene logike so obravnavani spodaj.

- Ima izjemno nizko mejo hrupa, tj. ±200 mV.

- Disipacija moči je visoka v primerjavi z drugimi logičnimi vrati.

- Za povezavo z drugimi logičnimi družinami so potrebni nivojski preklopniki.

- Ventilator omejuje kapacitivno obremenitev.

- V primerjavi z TTL , vrata ECL so draga.

- V primerjavi s CMOS in TTL je odpornost ECL na hrup najslabša.

Aplikacije

Aplikacije emitersko sklopljene logike vključujejo naslednje.

- Emitersko sklopljena logika se uporablja kot logika in vmesniška tehnologija v izjemno hitrih komunikacijskih napravah, kot so vmesniki sprejemnikov in oddajnikov z optičnimi vlakni, omrežja Ethernet in ATM (asinhroni način prenosa).

- ECL je logična družina, ki temelji na BJT, kjer je njegovo visoko hitrost delovanja mogoče doseči z uporabo razmeroma majhnega nihanja napetosti in izogibanjem prehodu tranzistorjev v območje nasičenosti.

- ECL se uporablja pri izdelavi vezij ASLT znotraj IBM 360/91.

- ECL se izogiba uporabi zloženih tranzistorjev z uporabo enosmerne prednapetosti i/p in pozitivne povratne zveze med primarnimi in sekundarnimi tranzistorji, da doseže funkcijo pretvornika.

- ECL se uporablja v izjemno hitri elektroniki.

Torej, to je pregled emitersko sklopljene logike ali ECL – vezje, delovanje, funkcije, karakteristike in aplikacije. ECL je najhitrejša logična družina, ki temelji na BJT v primerjavi z drugimi digitalnimi logičnimi družinami. Delovanje z največjo hitrostjo doseže z majhnim nihanjem napetosti in prepreči, da bi se tranzistorji premaknili v območje nasičenosti. Ta logična družina zagotavlja neverjetno 1ns propagacijsko zakasnitev in v najnovejših družinah ECL je ta zakasnitev zmanjšana. Tukaj je vprašanje za vas, kakšno je nadomestno ime za ECL?