Nabor navodil ali nabor ukazov je struktura računalnika, ki računalniku zagotavlja ukaze za vodenje računalnika za obdelavo podatkov. Nabor navodil je sestavljen iz navodil, načinov naslavljanja, izvornih podatkovnih tipov, registrov, prekinitev, obdelave izjem in arhitekture pomnilnika. Nabor navodil je mogoče posnemati v programski opremi z uporabo tolmača ali vgraditi v strojno opremo procesorja. Nabor navodil Arhitektura je lahko meja med programsko in strojno opremo. Klasifikacija mikrokrmilnikov in mikroprocesorje je mogoče izvesti na podlagi arhitekture nabora ukazov RISC in CISC.

Komplet navodil za procesor

Nabor navodil določa funkcionalnost procesorja, vključno z operacijami, ki jih podpira procesor, mehanizmi za shranjevanje procesorja in način sestavljanja programov v procesor.

Kaj sta RISC in CISC?

The RISC in CISC se lahko razširi na naslednji način:

RISC predstavlja računalnik z zmanjšanimi navodili in

CISC predstavlja kompleksni računalnik z navodili.

Arhitektura RISC (računalnik z zmanjšanimi navodili)

Arhitektura RISC

The arhitektura mikrokrmilnika ki uporablja majhen in zelo optimiziran nabor navodil, se imenuje računalnik z zmanjšanimi navodili ali preprosto RISC. Imenuje se tudi kot LOAD / STORE arhitektura.

V poznih sedemdesetih in zgodnjih osemdesetih letih so bili projekti RISC razviti predvsem od Stanforda, UC-Berkleyja in IBM-a. John Coke iz IBM-ove raziskovalne skupine je razvil RISC tako, da je zmanjšal število navodil, potrebnih za hitrejšo obdelavo izračunov kot CISC. Arhitektura RISC je hitrejša in čipi, potrebni za izdelavo arhitekture RISC, so tudi cenejši v primerjavi z arhitekturo CISC.

Tipične značilnosti RISC arhitekture

- Tehnika pipetiranja RISC izvaja več delov ali stopenj navodil hkrati, tako da je vsako navodilo na CPU optimizirano. Zato imajo procesorji RISC uro na navodilo enega cikla, kar se imenuje izvedba enega cikla.

- Optimizira uporaba registra z večjim številom registrov v RISC in večjim številom interakcij znotraj pomnilnika je mogoče preprečiti.

- Preprosti načini naslavljanja, tudi kompleksno naslavljanje je mogoče opraviti z uporabo aritmetike IN / ALI logične operacije .

- Poenostavlja zasnovo prevajalnika z uporabo enakih registrov splošnega namena, ki omogoča uporabo katerega koli registra v katerem koli kontekstu.

- Za učinkovito uporabo registrov in optimizacijo uporabe cevovodov je potreben zmanjšan nabor navodil.

- Število bitov, uporabljenih za opcode, se zmanjša.

- Na splošno je v RISC 32 ali več registrov.

Prednosti arhitekture procesorja RISC

- Zaradi majhnega nabora navodil RISC lahko visokokakovostni prevajalniki jezikov ustvarijo učinkovitejšo kodo.

- RISC omogoča svobodo uporabe prostora na mikroprocesorji zaradi svoje preprostosti.

- Namesto Stacka mnogi procesorji RISC uporabljajo registre za posredovanje argumentov in zadrževanje lokalnih spremenljivk.

- Funkcije RISC uporabljajo le nekaj parametrov, zato procesorji RISC ne morejo uporabljati navodil za klic, zato uporabljajo navodila z določeno dolžino, ki jih je enostavno napeljati.

- Hitrost operacije je mogoče maksimirati in čas izvedbe zmanjšati.

- Potrebno je zelo malo oblik navodil (manj kot štiri), nekaj navodil (približno 150) in nekaj načinov naslavljanja (manj kot štiri).

Pomanjkljivosti arhitekture procesorja RISC

- S povečanjem dolžine navodil se zapletenost za izvajanje procesorjev RISC poveča zaradi cikla znakov na ukaz.

- Delovanje procesorjev RISC je odvisno predvsem od prevajalnika ali programerja, saj ima znanje prevajalnika pomembno vlogo pri pretvorbi kode CISC v kodo RISC, zato je kakovost ustvarjene kode odvisna od prevajalnika.

- Med prerazporeditvijo kode CISC na kodo RISC, imenovano razširitev kode, se bo povečala velikost. Kakovost razširitve kode bo spet odvisna od prevajalnika in tudi od nabora navodil računalnika.

- Predpomnilnik prve stopnje procesorjev RISC je tudi pomanjkljivost sistema RISC, v katerem imajo ti procesorji velik pomnilnik na samem čipu. Za hranjenje navodil potrebujejo zelo hitri pomnilniški sistemi .

Arhitektura CISC (Computer Inset Set Computer)

Glavni namen arhitekture procesorja CISC je dokončati nalogo z uporabo manjšega števila montažnih linij. V ta namen je procesor zgrajen za izvajanje vrste operacij. Kompleksna navodila se imenujejo tudi MULT, ki delujejo pomnilniške banke računalnika neposredno, ne da bi prevajalnik izvajal funkcije shranjevanja in nalaganja.

Arhitektura CISC

Značilnosti arhitekture CISC

- Za poenostavitev računalniške arhitekture CISC podpira mikroprogramiranje.

- CISC ima več vnaprej določenih navodil, kar olajša oblikovanje in izvajanje jezikov na visoki ravni.

- CISC je sestavljen iz manjšega števila registrov in večjega števila načinov naslavljanja, običajno od 5 do 20.

- Procesor CISC potrebuje različen čas cikla za izvajanje navodil - več urni cikli.

- Zaradi zapletenega nabora navodil CISC je tehnika cevovoda zelo težka.

- CISC vsebuje več navodil, običajno od 100 do 250.

- Posebna navodila se uporabljajo zelo redko.

- Z operandi v spominu se upravlja z navodili.

Prednosti arhitekture CISC

- Vsako navodilo strojnega jezika je združeno v navodilo mikrokode in ustrezno izvedeno, nato pa je vgrajeno v pomnilnik glavnega procesorja, ki se imenuje izvajanje mikrokode.

- Ker je pomnilnik mikrokode hitrejši od glavnega pomnilnika, je mogoče nabor navodil za mikrokode izvajati brez bistvenega zmanjšanja hitrosti pri trdi žični izvedbi.

- S spreminjanjem zasnove mikro programa lahko obdelate celoten nov nabor ukazov.

- CISC lahko število navodil, potrebnih za izvajanje programa, zmanjšamo z gradnjo bogatih naborov ukazov, lahko pa tudi za učinkovitejšo uporabo počasnega glavnega pomnilnika.

- Zaradi nabora navodil, ki je sestavljen iz vseh prejšnjih navodil, to olajša mikro kodiranje.

Pomanjkljivosti CISC

- Količina ure, ki jo uporabljajo različna navodila, bo različna - zaradi tega se delovanje naprave upočasni.

- Zapletenost nabora navodil in strojna oprema čipa se povečuje, saj je vsaka nova različica procesorja sestavljena iz podskupine prejšnjih generacij.

- Le 20% obstoječih navodil se uporablja v običajnem programskem dogodku, čeprav obstaja veliko specializiranih navodil, ki se niti ne uporabljajo pogosto.

- Pogojne kode so v navodilih CISC nastavljene kot stranski učinek vsakega ukaza, ki za to nastavitev potrebuje čas - in ker naslednje navodilo spreminja bitov kode pogoja - mora torej prevajalnik preučiti bitove kode pogoja, preden se to zgodi.

RISC Vs. CISC

- Programerje lahko programerji prepreči z zapravljanjem, tako da odstrani nepotrebno kodo v RISC, vendar pa uporaba kode CISC zaradi neučinkovitosti CISC vodi do zapravljanja ciklov.

- V RISC je vsako navodilo namenjeno izvajanju majhne naloge, tako da se za izvedbo zapletene naloge uporablja več majhnih navodil skupaj, medtem ko je za izvedbo iste naloge s pomočjo CISC potrebnih le nekaj navodil, saj je sposobna izvajati zapleteno nalogo saj so navodila podobna visokojezični kodi.

- CISC se običajno uporablja za računalnike, medtem ko se RISC uporablja za pametne telefone, tablice in druge elektronske naprave.

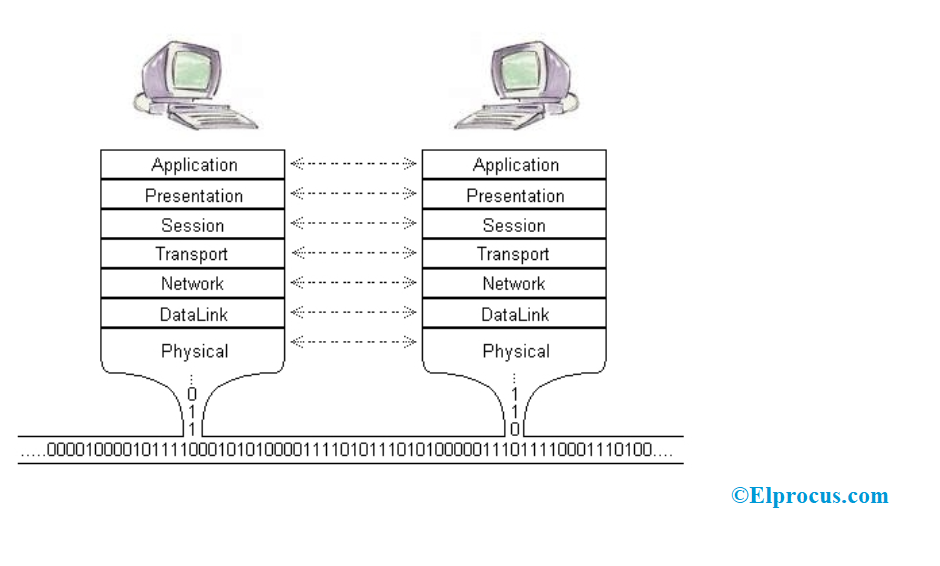

Naslednja slika prikazuje več razlik med RISC in CISC

RISC Vs. CISC

Tako ta članek razpravlja o značilnostih arhitektur RISC in CISC, značilnostih arhitekture procesorjev RISC in CISC, prednostih in pomanjkljivostih RISC in CISC ter o razlikah med arhitekturama RISC in CISC s kratko idejo. Če želite več informacij o arhitekturah RISC in CISC, objavite svoja vprašanja tako, da komentirate spodaj.

Zasluge za fotografije:

- Komplet navodil za procesor arstechnica

- Arhitektura RISC avtor lsi-natečaj

- RISC v primerjavi s CISC avtorja dodelitev