Povečanje hitrosti izvajanja programa posledično povečuje hitrost procesor. Obstaja veliko izumljenih načinov, tako za izvedbo strojne opreme kot za arhitekturo programske opreme, za povečanje hitrosti izvajanja. Ugotovljeno je bilo, da se lahko s sočasnim izvajanjem navodil skrajša čas, potreben za izvedbo. Koncept paralelizma v Ljubljani programiranje je bil predlagan. V skladu s tem je mogoče na en urni cikel izvesti več kot eno navodilo. Ta koncept lahko izvaja programer z različnimi tehnikami, kot so Cevovodi, več izvedbenih enot in več jeder . Med vsemi temi metodami vzporednosti se najpogosteje izvaja cevovod. Kako se torej lahko izvede navodilo pri metodi cevovoda? Kako poveča hitrost izvedbe?

Kaj je cevovod?

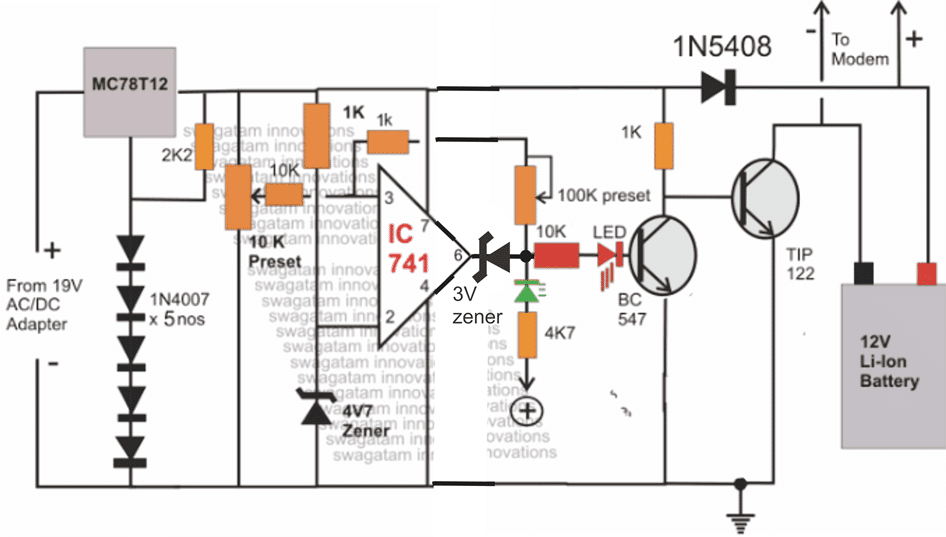

Da bi razumeli koncept cevovoda, si oglejmo korensko raven izvajanja programa. Navodilo je najmanjši izvedbeni paket programa. Vsako navodilo vsebuje eno ali več operacij. Preprosti skalarni procesorji izvršijo eno ali več ukazov na urni cikel, pri čemer vsako ukaz vsebuje samo eno operacijo. Navodila se izvajajo kot zaporedje faz, da se dosežejo pričakovani rezultati. To zaporedje je navedeno spodaj

Zaporedje izvrševanja navodil

- IF: Naloži navodilo v register navodil.

- ID: Instruction Decode, dekodira navodila za kodo op.

- AG: Generator naslovov, ustvari naslov.

- DF: Data Fetch, pridobi operande v podatkovni register.

- EX: Izvedba, izvede določeno operacijo.

- WB: Zapiši nazaj, rezultat zapiše nazaj registra.

Vsa navodila ne zahtevajo vseh zgornjih korakov, vendar jih večina zahteva. Ti koraki uporabljajo različne funkcije strojne opreme. Pri cevovodu se te različne faze izvajajo sočasno. Pri pripravi cevovodov se te faze med različnimi operacijami štejejo za neodvisne in se lahko prekrivajo. Tako je mogoče hkrati izvajati več operacij, pri čemer je vsaka operacija v svoji neodvisni fazi.

Navodilo cevovodi

Oglejmo si način obdelave navodil pri cevovodu. To lahko enostavno razumemo s spodnjim diagramom.

Navodilo cevovodi

Predpostavimo, da so navodila neodvisna. V preprostem procesorju cevovoda je v določenem času v vsaki fazi samo ena operacija. Začetna faza je faza IF. Torej, v prvem urnem ciklu se pridobi ena operacija. Ko prispe naslednji impulz ure, prva operacija preide v fazo ID, pri čemer ostane faza IF prazna. Zdaj je ta prazna faza dodeljena naslednji operaciji. Torej, med drugim taktnim impulzom je prva operacija v fazi ID, druga operacija pa v fazi IF.

Za tretji cikel bo prva operacija v fazi AG, druga operacija bo v fazi ID in tretja operacija bo v fazi IF. Na ta način se navodila izvajajo sočasno in po šestih ciklih bo procesor izdal popolnoma izvršeno navodilo na urni cikel.

Ali se to navodilo izvaja zaporedno, prvo navodilo mora iti skozi vse faze, nato pa bi bilo naloženo naslednje navodilo? Za izvajanje vsakega ukaza bi torej procesor potreboval šest urnih ciklov. Toda v cevovodnem procesorju, ker izvajanje navodil poteka sočasno, samo začetno navodilo zahteva šest ciklov, vsa preostala navodila pa se izvedejo po eno na vsak cikel, s čimer se skrajša čas izvajanja in poveča hitrost procesorja.

Cevovodna arhitektura

Vzporednost je mogoče doseči s strojno opremo, prevajalnikom in tehnikami programske opreme. Da bi izkoristili koncept cevovoda v računalniška arhitektura veliko procesorskih enot je medsebojno povezanih in delujejo hkrati. V cevovodni arhitekturi procesorja so za števila in navodila s plavajočo vejico na voljo ločene procesne enote. Medtem ko je v zaporedni arhitekturi predvidena ena funkcionalna enota.

Cevovodna procesorska enota

Pri statičnem cevovodu naj procesor posreduje navodila skozi vse faze cevovoda, ne glede na zahteve po navodilih. V dinamičnem procesorju cevovoda lahko navodilo zaobide faze, odvisno od svoje zahteve, vendar se mora premikati v zaporednem vrstnem redu. V kompleksnem procesorju dinamičnega cevovoda lahko navodilo zaobide faze in izbere faze, ki niso v redu.

Vodovod v procesorjih RISC

Najbolj popularen RISC arhitektura Procesor ARM sledi 3-stopenjskemu in 5-stopenjskemu cevovodu. V 3-stopenjskem cevovodu so faze: Fetch, Decode in Execute. Ta cevovod ima 3 zakasnitve, saj posamezno navodilo potrebuje 3 urne cikle.

ARM 3-stopenjski cevovod

Za pravilno izvedbo cevovoda je treba nadgraditi tudi arhitekturo strojne opreme. Strojna oprema za 3-stopenjsko cevovod vključuje registrsko banko, ALU, Barrel Shift, generator naslovov, inkrement, dekodirnik navodil in registre podatkov.

Podatkovna pot ARM 3 stopnje

V petih stopnjah so stopnjevanje: Factch, Decode, Execute, Buffer / data in Write back

Nevarnosti cevovoda

V običajnem računalniškem programu poleg preprostih navodil obstajajo navodila za veje, prekinitve, branje in pisanje navodil. Cevovodi niso primerni za vse vrste navodil. Ko se nekatera navodila izvedejo pri cevovodu, lahko cevovod ustavijo ali popolnoma izperejo. Tovrstne težave, ki nastanejo med cevovodom, se imenujejo nevarnosti cevovodov.

V večini računalniških programov se rezultat enega navodila uporabi kot operand drugega navodila. Ko se taka navodila izvajajo v cevovodu, pride do razčlenitve, ker rezultat prvega navodila ni na voljo, ko začne drugo navodilo zbirati operande. Torej, ukaz dva mora zastajati, dokler se ukaz 1 ne izvrši in rezultat se ustvari. Ta vrsta nevarnosti se imenuje nevarnost branja - naknadnega zapisovanja.

Nevarnost pipetiranja po branju po pisanju

Izvrševanje navodil za podružnice povzroča tudi nevarnost cevovoda. Navodila za vejo med izvajanjem v cevovodu vpliva na faze pridobivanja naslednjih navodil.

Obnašanje vejnih vodov

Prednosti cevovoda

- Poveča se pretočnost navodil.

- Povečanje števila stopenj cevovoda poveča število hkrati izvedenih navodil.

- Hitrejši ALU je mogoče oblikovati, kadar se uporablja cevovod.

- Pipelined CPU deluje na višjih taktnih frekvencah kot RAM.

- Cevovod povečuje splošno zmogljivost CPU.

Slabosti cevovodov

- Oblikovanje cevovodnega procesorja je zapleteno.

- Poveča se zakasnitev navodil pri cevovodnih procesorjih.

- Prepustnost cevovodnega procesorja je težko napovedati.

- Daljši je cevovod, še večja je nevarnost navodil za odcepe.

Pipeliranje koristi vsem navodilom, ki sledijo podobnemu zaporedju korakov za izvedbo. Procesorje z zapletenimi navodili, pri katerih se vsaka navodila obnašajo drugače, je težko napeljati. Predelovalci imajo primerne naprave s 3 ali 5 stopnjami cevovoda, saj se z globino cevovoda nevarnosti, povezane z njim, povečujejo. Navedite nekatere cevovodne procesorje s stopnjo cevovoda?