The tranzistor s poljskim učinkom (FET) je elektronska naprava, v kateri je električno polje se uporablja za uravnavanje pretoka toka. Da bi to izvedli, se potencialna razlika uporabi na terminalih vrat in vira naprave, kar spremeni prevodnost med odtokom in virom, zaradi česar čez te terminale teče nadzorovani tok.

Imenujejo se FET enopolarni tranzistorji ker so zasnovani za delovanje kot naprave z enim nosilcem. Na voljo so različne vrste tranzistorjev z efektom polja.

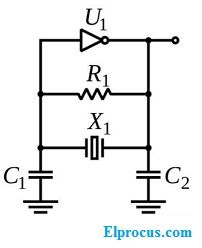

Simbol

Grafični simboli za n-kanalne in p-kanalne JFET-je so lahko prikazani na naslednjih slikah.

Jasno lahko opazite, da puščice, ki kažejo navznoter za n-kanalno napravo, označujejo smer, v katero IG(tok vrat) naj bi tekel, ko je bil p-n križišče prednaklonjeno.

Pri p-kanalni napravi so pogoji enaki, razen razlike v smeri puščice.

Razlika med FET in BJT

Tranzistor s poljskim učinkom (FET) je triselna naprava, zasnovana za široko paleto aplikacij vezja, ki v veliki meri dopolnjujejo tiste BJT tranzistorja.

Medtem ko boste našli pomembne razlike med BJT in JFET, obstaja dejansko več ujemajočih se značilnosti, o katerih bomo govorili v naslednjih razpravah. Glavna razlika med temi napravami je BJT tokovno krmiljena naprava, kot je prikazana na sliki 5.1a, medtem ko je tranzistor JFET napetostno krmiljena naprava, kot je prikazano na sliki 5.1b.

Preprosto povedano, sedanji ICna sliki 5.1a je neposredna funkcija ravni IB. Za FET je tok I funkcija napetosti VGSpodana vhodnemu vezju, kot je prikazano na sliki 5.1b.

V obeh primerih bo tok izhodnega vezja urejen s parametrom vhodnega vezja. V enem primeru trenutna raven, v drugem pa uporabljena napetost.

Tako kot npn in pnp za bipolarne tranzistorje boste našli n-kanalne in p-kanalne tranzistorje z efektom polja. Ne pozabite pa, da je BJT tranzistor bipolarna naprava, ki predpona bi-označuje, da je raven prevodnosti funkcija dveh nosilcev naboja, elektronov in lukenj.

FET pa je enopolarna naprava to je odvisno izključno od prevodnosti elektronov (n-kanal) ali luknje (p-kanal).

Besedno zvezo „poljski učinek“ lahko razložimo tako: vsi se zavedamo moči trajnega magneta, da pritegne kovinske opilke proti magnetu brez kakršnega koli fizičnega stika. Popolnoma na podoben način znotraj FET-a ustvarijo električno polje obstoječi naboji, ki vplivajo na prevodno pot izhodnega vezja, ne da bi imeli neposreden stik med nadzornimi in nadzorovanimi količinami. Verjetno ena najpomembnejših lastnosti FET-a je njegova visoka vhodna impedanca.

V območju od 1 do več sto megohmov znatno presega običajna območja vhodnega upora pri konfiguracijah BJT, kar je izjemno pomembna lastnost pri razvoju modelov linearnih ojačevalnikov.

Vendar ima BJT večjo občutljivost na spremembe vhodnega signala. To pomeni, da je sprememba izhodnega toka pri BJT-jih običajno bistveno večja kot pri FET-ih za enako količino spremembe njihovih vhodnih napetosti.

Zaradi tega so lahko standardni ojačevalniki izmenične napetosti za ojačevalnike BJT veliko višji v primerjavi s FET-ji.

Na splošno so FET-ji bistveno bolj toplotno odporni kot BJT-ji in so pogosto manjši po strukturi v primerjavi z BJT-ji, zaradi česar so posebej primerni za vgradnjo kot integrirano vezje (IC)čips.

Po drugi strani pa lahko strukturne značilnosti nekaterih FET-jev omogočajo, da so izjemno občutljivi na fizične stike kot BJT-ji.

Več BJT / JFET razmerja

- Za BJT VBODI= 0,7 V je pomemben dejavnik za začetek analize njegove konfiguracije.

- Podobno je parameter IG= 0 A je običajno prva stvar, ki jo upoštevamo pri analizi vezja JFET.

- Za konfiguracijo BJT sem IBje pogosto prvi dejavnik, ki ga je treba določiti.

- Podobno je za JFET običajno VGS.

V tem članku se bomo osredotočili na JFET-je ali tranzistorje z efektom spojnega polja, v naslednjem članku pa bomo razpravljali o tranzistorju s poljskim efektom kovinski oksid-polprevodnik ali MOS-FET.

KONSTRUKCIJA IN ZNAČILNOSTI JFET

Kot smo se naučili, ima JFET 3 vodila. Eden od njih nadzoruje tok toka med drugima dvema.

Tako kot BJT-ji se tudi v JFET-jih n-kanalna naprava uporablja bolj vidno kot p-kanalni kolegi, saj je n naprav bolj učinkovitih in uporabnikom prijaznejših v primerjavi s p-napravami.

Na naslednji sliki lahko vidimo osnovno strukturo ali konstrukcijo n-kanalnega JFET-a. Vidimo lahko, da sestava tipa n tvori glavni kanal v slojih tipa p.

Zgornji del kanala tipa n je prek omskega kontakta povezan s priključkom, imenovanim odtok (D), medtem ko je spodnji del istega kanala prek ohmičnega kontakta povezan tudi z drugim terminalom, imenovanim vir (S).

Nekaj materialov tipa p je povezanih s terminalom, imenovanim vrata (G). V bistvu ugotovimo, da sta odtočna in izvorna sponka združena na koncih kanala tipa n. Vrata spojena na par p-kanalnih materialov.

Ko na jfetu ni napetosti, sta njegova dva p-n križišča brez kakršnih koli pristranskih pogojev. V tej situaciji obstaja območje izčrpavanja na vsakem križišču, kot je prikazano na zgornji sliki, ki je povsem podobno diodni p-n regiji brez pristranskosti.

Analogija vode

Delovanje in nadzor JFET-a je mogoče razumeti z naslednjo analogijo z vodo.

Tu lahko tlak vode primerjamo z velikostjo uporabljene napetosti od odtoka proti viru.

Pretok vode lahko primerjamo s pretokom elektronov. Ustje pipe posnema izvorni priključek JFET-a, medtem ko zgornji del pipe, kamor je prisiljena voda, prikazuje odtok JFET-a.

Gumb za pipe deluje kot Vrata JFET-a. S pomočjo vhodnega potenciala nadzoruje pretok elektronov (naboj) od odtoka do vira, tako kot gumb za odtok nadzoruje pretok vode v odprtini ust.

Iz strukture JFET lahko vidimo, da sta odtočna in izvorna sponka na nasprotnih koncih n-kanala, in ker izraz temelji na elektronskem toku, lahko zapišemo:

VGS= 0 V, VDSNekaj pozitivne vrednosti

Na sliki 5.4 lahko vidimo pozitivno napetost VDSuporabljen preko n-kanala. Vhodni terminal je neposredno povezan z virom, da se ustvari pogoj VGS= 0V. To omogoča, da imajo priključki in izvorni terminali enak potencial, kar povzroči nižje območje izpraznitve vsakega p-materiala, natančno tako, kot vidimo na prvem diagramu zgoraj, brez pogojev.

Takoj, ko napetost VDD(= VDS), se elektroni potegnejo proti odtočnemu priključku in ustvarijo običajni tok tokovnega ID, kot je prikazano na sliki 5.4.

Smer toka naboja razkriva, da sta odtočni in izvorni tok enako velika (ID= JazS). Glede na pogoje, prikazane na sliki 5.4, je pretok naboja videti precej neomejen in nanj vpliva le upor n-kanala med odtokom in izvorom.

Opazite, da je območje izčrpavanja večje okoli zgornjega dela obeh materialov tipa p. Ta razlika v velikosti regije je v idealnem primeru razložena na sliki 5.5. Predstavljajmo si, da imamo enak upor v n-kanalu, ki bi ga lahko razdelili na odseke, prikazane na sliki 5.5.

Sedanji IDlahko gradi napetostni razpon skozi kanal, kot je poudarjeno na isti sliki. Kot rezultat bo zgornje območje materiala tipa p obrnjeno za približno 1,5 V, spodnje območje pa le za 0,5 V.

Točka, da je p-n križišče vzvratno pristransko vzdolž celotnega kanala, povzroči tok v vratih z ničelnimi amperi, kot je prikazano na isti sliki. Ta značilnost, ki vodi do IG= 0 A je pomembna značilnost JFET.

Kot VDSpotencial se poveča z 0 na nekaj voltov, tok se poveča v skladu z Ohmovim zakonom in grafikonom IDvrstica 5DSlahko izgleda, kot je dokazano na sliki 5.6.

Primerjalna naravnost risanja kaže, da je za območja z nizko vrednostjo VDS, upor je v osnovi enakomeren. Kot VDSse dvigne in približa ravni, ki je na sliki 5.6 znana kot VP, se območja izčrpavanja širijo, kot je prikazano na sliki 5.4.

Posledica tega je očitno znižanje širine kanala. Zmanjšana prevodna pot vodi do povečanja upora, kar povzroči krivuljo na sliki 5.6.

Bolj ko je krivulja vodoravna, večji je upor, kar kaže, da se upor v vodoravnem območju povečuje proti 'neskončnim' ohmom. Ko je VDSpoveča do te mere, da bi se izkazalo, da bi se lahko območji izčrpavanja 'stikali', kot je prikazano na sliki 5.7, in nastane situacija, znana kot pinch-off.

Znesek, za katerega VDSse ta situacija imenuje pinch-off napetost in jo simbolizira VPkot je prikazano na sliki 5.6. Na splošno je beseda pinch-off zavajajoča, ker pomeni trenutni IDje 'odščipnjen' in pade na 0 A. Kot je dokazano na sliki 5.6, to v tem primeru komajda očitno. jazDohrani raven nasičenosti, označeno z IDSSna sliki 5.6.

Resnica je, da še vedno obstaja zelo malo kanalov, ki imajo tok zelo visoke koncentracije.

Točka, pri kateri ID ne pade pinch-off in ohranja raven nasičenosti, kot je prikazano na sliki 5.6, se potrdi z naslednjim dokazom:

Ker ni odtočnega toka, s pomočjo materiala n-kanala odpravlja možnost različnih potencialnih ravni za določanje spreminjajočih se količin povratne pristranskosti vzdolž p-n križišča. Končni rezultat je izguba distribucije območja izčrpavanja, ki je sprožila pinch-off za začetek.

Ko povečujemo VDSnad VP, območje tesnega stika, kjer se bosta obe območji izčrpavanja med seboj srečali, se vzdolž kanala poveča. Vendar raven osebnih podatkov ostaja v bistvu nespremenjena.

Tako je trenutek VDSje višja od Vstr, JFET pridobi značilnosti trenutnega vira.

Kot je dokazano na sliki 5.8, je tok v JFET določen pri ID= JazDSS, toda napetost VDSvišja od VP je določena s priključeno obremenitvijo.

Izbira zapisa IDSS temelji na dejstvu, da ima tok odtok do vira kratkostično povezavo čez vrata do vira.

Nadaljnja preiskava nam da naslednjo oceno:

jazDSSje najvišji odtočni tok za JFET in je določen v pogojih VGS= 0 V in VDS> | VP |.

Upoštevajte, da je na sliki 5.6 VGSje 0V za celoten odsek krivulje. V naslednjih razdelkih bomo izvedeli, kako vplivajo atributi slike 5.6 kot raven VGSje raznolika.

VGS <0V

Volatiranje, ki se uporablja prek vrat in vira, je označeno kot VGS, ki je odgovoren za nadzor delovanja JFET.

Če vzamemo primer BJT, tako kot krivulje ICproti VTOso določene za različne ravni IB, podobno krivulje IDproti VDSza različne ravni VGSje mogoče ustvariti za primer JFET.

V ta namen je nastavljen vhodni terminal na nižji potencial pod nivojem potenciala vira.

Sklicujoč se na sliko 5.9 spodaj, se -1V uporablja preko terminalov vrat / vira za zmanjšano VDSravni.

Cilj negativne potencialne pristranskosti VGSje razviti izčrpane regije, podobne položaju V.GS= 0, vendar pri bistveno zmanjšanem VDS.

To povzroči, da vrata dosežejo točko nasičenja z nižjimi nivoji VDSkot je prikazano na sliki 5.10 (VGS= -1V).

Ustrezna stopnja nasičenosti za IDlahko ugotovimo, da se zmanjšuje in se dejansko kar zmanjšuje, ko VGSje bolj negativna.

Na sliki 5.10 lahko jasno vidite, kako se odklopna napetost še naprej spušča s parabolično obliko kot VGSpostane vedno bolj negativno.

Končno, ko je VGS= -Vstr, postane dovolj negativen za določitev nasičenosti, ki je sčasoma 0 mA. Na tej ravni je JFET popolnoma 'izklopljen'.

Raven VGSkar povzroča IDza doseganje 0 mA je značilen VGS= VPkjer je VPje negativna napetost za n-kanalne naprave in pozitivna napetost za p-kanalne JFET-je.

Običajno lahko najdete večino podatkovnih listov JFET pinch-off napetost, določena kot VGS (izključeno)namesto VP.

Območje na desni strani lopute na zgornji sliki je mesto, ki se običajno uporablja v linearnih ojačevalnikih za doseganje signala brez popačenja. Ta regija se na splošno imenuje območje konstantnega toka, nasičenja ali linearnega ojačanja.

Napetostno krmiljeni upor

Območje na levi strani lopute na isti sliki se imenuje ohmično območje ali napetostno nadzorovano odporno območje.

V tej regiji lahko napravo dejansko upravljamo s spremenljivim uporom (na primer v aplikaciji za samodejno krmiljenje ojačenja), pri čemer njen upor nadzorujemo prek uporabljenega potenciala vrat / vira.

Vidite lahko, da je naklon vsake krivulje, ki pomeni tudi upor odtoka / vira JFET za VDS

Ko povečujemo VGS z negativnim potencialom, postaja naklon vsake krivulje vedno bolj vodoraven, kar kaže na sorazmerno povečanje ravni upora.

Z naslednjo enačbo lahko dobimo dober začetni približek ravni upora glede na napetost VGS.

p-Channel JFET deluje

Notranja postavitev in konstrukcija p-kanalnega JFET je popolnoma enaka n-kanalni dvojici, le da sta področji materialov p- in n-tipa obrnjeni, kot je prikazano spodaj:

Smeri toka toka lahko vidimo tudi kot obratno, skupaj z dejanskimi polaritetami napetosti VGS in VDS. V primeru p-kanalnega JFET bo kanal omejen kot odgovor na povečanje pozitivnega potenciala skozi vrata / vir.

Zapis z dvojnim podpisom za VDSbo povzročil negativno napetost za VDS, kot je prikazano na značilnostih slike 5.12. Tu lahko najdete jazDSSpri 6 mA, medtem ko je odklopna napetost pri VGS= + 6V.

Prosim, ne zmedite se zaradi prisotnosti znaka thee minus za VDS. To preprosto kaže, da ima vir večji potencial kot odtok.

Vidite, da krivulje za visoko VDSravni se nenadoma dvignejo na vrednosti, ki so videti neomejene. Označeni vzpon, ki je navpičen, simbolizira stanje okvare, kar pomeni, da tok v kanalski napravi v tem trenutku v celoti nadzoruje zunanje vezje.

Čeprav to na sliki 5.10 za n-kanalno napravo ni razvidno, je to morda pod dovolj visoko napetostjo.

To območje je mogoče odpraviti, če VDS (največ)je zapisano v obrazcu naprave, naprava pa je konfigurirana tako, da dejanski VDSvrednost je nižja od omenjene vrednosti za kateri koli VGS.

Prejšnja: 5 najboljših raziskovanih vezij z močjo 40 W Naprej: Podatkovni list 2N3055, Pinout, aplikacijska vezja