Bilo je obdobje, ko so bili računalniki tako veliki, da so bili za njihovo namestitev potrebni prostori v sobi. Danes pa so tako razviti, da jih lahko celo enostavno nosimo kot zvezke. Novost, ki je to omogočila, je bil koncept integriranih vezij. V Integrirana vezja , veliko število aktivnih in pasivni elementi skupaj z njihovimi medsebojnimi povezavami se razvijejo v majhni silicijevi rezini, ki je običajno v prerezu 50 x 50 mil. Osnovni postopki, ki so bili uporabljeni za izdelavo tovrstnih vezij, vključujejo epitaksialno rast, prikrito difuzijo nečistoč, rast oksida in jedkanje oksidov z uporabo fotolitografije za izdelavo vzorca.

Sestavni deli nad rezinami vključujejo upore, tranzistorje, diode, kondenzatorje itd. Najbolj zapleten element za izdelavo IC je tranzistor. Tranzistorji so različnih vrst kot so CMOS, BJT, FET. Glede na zahteve izberemo vrsto tranzistorske tehnologije, ki jo bomo implementirali prek IC. V tem članku se seznanimo s konceptom Izdelava CMOS (ali) izdelava tranzistorjev kot CMOS.

Izdelava CMOS

Za manjšo porabo energije Tehnologija CMOS se uporablja za izvajanje tranzistorjev. Če potrebujemo hitrejše vezje, so tranzistorji nameščeni IC z uporabo BJT . Izdelava Tranzistorji CMOS saj se IC lahko izvede na tri različne načine.

Tehnologija N-well / P-well, pri kateri se difuzija n-tipa izvaja na substratu p-tipa, difuzija p-tipa pa na substratu n-tipa.

The Tehnologija dvojnih vrtin , kje NMOS in tranzistor PMOS se razvijejo nad rezinami s hkratno difuzijo nad epitaksialno rastno podlago in ne podlogo.

Postopek silicijevega izolatorja, pri katerem se izolacijski material, namesto da bi uporabil silicij kot podlago, uporabi za izboljšanje hitrosti in občutljivosti zaklepanja.

Tehnologija N- / P-well

CMOS lahko dobimo z integracijo obeh Tranzistorji NMOS in PMOS preko iste silicijeve rezine. V tehnologiji N-vrtin se vodnjak tipa n razprši na podlagi tipa p, medtem ko je v vrtini P obratno.

Koraki izdelave CMOS

The Postopek izdelave CMOS pretok se izvaja z uporabo dvajsetih osnovnih korakov izdelave, medtem ko se proizvaja z uporabo tehnologije N-well / P-well.

Izdelava CMOS z uporabo N dobro

Korak 1: Najprej izberemo podlago kot podlago za izdelavo. Za N-vodnjak je izbran silikonski substrat tipa P.

Podlaga

2. korak - oksidacija: Selektivna difuzija nečistoč tipa n se doseže z uporabo SiO2 kot pregrade, ki ščiti dele rezin pred kontaminacijo podlage. SiOdvaje razstavljen s postopkom oksidacije, ki je narejen tako, da se substrat izpostavi visokokakovostnemu kisiku in vodiku v oksidacijski komori pri približno 10000c

Oksidacija

3. korak - Gojenje Photoresista: Na tej stopnji, da se omogoči selektivno jedkanje, se plast SiO2 podvrže postopku fotolitografije. Pri tem je rezina prevlečena z enakomernim filmom fotoobčutljive emulzije.

Gojenje Photoresista

4. korak - maskiranje: Ta korak je nadaljevanje postopka fotolitografije. V tem koraku se s šablono naredi želeni vzorec odprtosti. Ta šablona se uporablja kot maska nad fotorezistom. Podlaga je zdaj izpostavljena UV žarki fotorezist, ki je prisoten pod izpostavljenimi predeli maske, se polimerizira.

Maskiranje fotoresista

5. korak - Odstranjevanje neosvetljenega fotorezista: Masko odstranimo in nerazpostavljeno področje fotorezista raztopimo z razvojem rezin z uporabo kemikalije, kot je trikloroetilen.

Odstranitev Photoresista

6. korak - jedkanje: Oblat je potopljen v jedkalno raztopino fluorovodikove kisline, ki odstranjuje oksid s površin, skozi katere naj se razpršijo dopanti.

Jedkanje SiO2

Korak 7 - Odstranjevanje celotne plasti Photoresist: Med postopek jedkanja , na tiste dele SiO2, ki so zaščiteni s plastjo fotoodpornosti, to ne vpliva. Masko s fotorezistom zdaj odstranimo s kemičnim topilom (vroč H2SO4).

Odstranjevanje sloja Photoresist

Korak 8 - Oblikovanje N-vodnjaka: Nečistoče tipa n se skozi izpostavljeno območje razpršijo v substrat tipa p in tako tvorijo vodnjak N.

Nastanek N-vodnjaka

Korak 9 - Odstranjevanje SiO2: Zdaj se plast SiO2 odstrani s fluorovodikovo kislino.

Odstranjevanje SiO2

10. korak - Nanašanje polisilicija: Neusmeritev vrat a Tranzistor CMOS bi privedlo do neželene kapacitivnosti, ki bi lahko škodovala vezju. Da bi preprečili ta 'postopek samonaravnavanja vrat', je prednostno, če se vrata oblikujejo pred tvorbo vira in odtoka z ionsko implantacijo.

Nanašanje polisilicija

Polisilicij se uporablja za oblikovanje vrat, saj lahko prenese visoke temperature nad 80000c kadar je rezina izpostavljena metodam žarjenja za oblikovanje vira in odtoka. Polisilicij se odlaga z uporabo Postopek kemičnega nanašanja nad tanko plastjo oksida vrat. Ta tanek oksid vrat pod plastjo polisilicija preprečuje nadaljnje dopiranje pod območjem vrat.

11. korak - Oblikovanje vratne regije: Razen dveh regij, potrebnih za oblikovanje vrat za Tranzistorji NMOS in PMOS preostali del polisilicija se odstrani.

Oblikovanje vratne regije

Korak 12 - Oksidacijski postopek: Oksidacijska plast se nanese na rezino, ki deluje kot ščit za nadaljnje delo postopki difuzije in metalizacije .

Postopek oksidacije

Korak 13 - Maskiranje in difuzija: Za izdelavo regij za difuzijo nečistoč tipa n s postopkom maskiranja so narejene majhne reže.

Maskiranje

Z uporabo difuzijskega procesa se razvijejo tri n + regije za tvorbo terminalov NMOS.

N-difuzija

14. korak - odstranjevanje oksida: Oksidna plast se odstrani.

Odstranjevanje oksida

Korak 15 - Difuzija tipa P: Podobno kot pri difuziji n-tipa se tvorijo terminali PMOS-ove difuzije p.

Difuzija tipa P

Korak 16 - Polaganje oksida iz debelih polj: Pred oblikovanjem kovinskih sponk se položi oksid z debelim poljem, ki tvori zaščitni sloj za področja rezin, kjer terminali niso potrebni.

Debelo oksidni sloj

Korak 17 - Metalizacija: Ta korak se uporablja za oblikovanje kovinskih sponk, ki lahko zagotavljajo medsebojne povezave. Aluminij se razprostira po celotni rezini.

Metalizacija

Korak 18 - Odstranjevanje odvečne kovine: Odvečna kovina se odstrani iz rezine.

Korak 19 - Oblikovanje terminalov: V režah, ki nastanejo po odstranitvi odvečnih kovinskih sponk, so oblikovane povezave.

Oblikovanje terminalov

20. korak - Dodelitev imen terminalov: Imena so dodeljena terminalom Tranzistorji NMOS in PMOS .

Dodelitev imen terminalov

Izdelava CMOS z uporabo tehnologije P well

Postopek p-vrtine je podoben postopku N-vrtin, le da se tu uporablja substrat n-tipa in se izvajajo difuzije p-tipa. Zaradi enostavnosti je navadno zaželen N proces.

Izdelava dvojne cevi CMOS

Z dvocevnim postopkom lahko nadzorujemo ojačanje naprav tipa P in N. Različni koraki, vključeni v izdelava CMOS z uporabo dvojne cevi so naslednji

- Vzamemo rahlo dopiran substrat tipa n ali p in uporabimo epitaksialni sloj. Epitaksialna plast ščiti problem zaskočenja v čipu.

- Gojijo se silicijeve plasti visoke čistosti z izmerjeno debelino in natančno koncentracijo dopata.

- Oblikovanje cevi za vodnjak P in N.

- Tanka oksidna konstrukcija za zaščito pred kontaminacijo med difuzijskimi procesi.

- Izvor in odtok nastanejo z uporabo metod ionske implantacije.

- Izrezi so narejeni za izdelavo delov za kovinske kontakte.

- Za vlečenje kovinskih kontaktov se opravi metalizacija

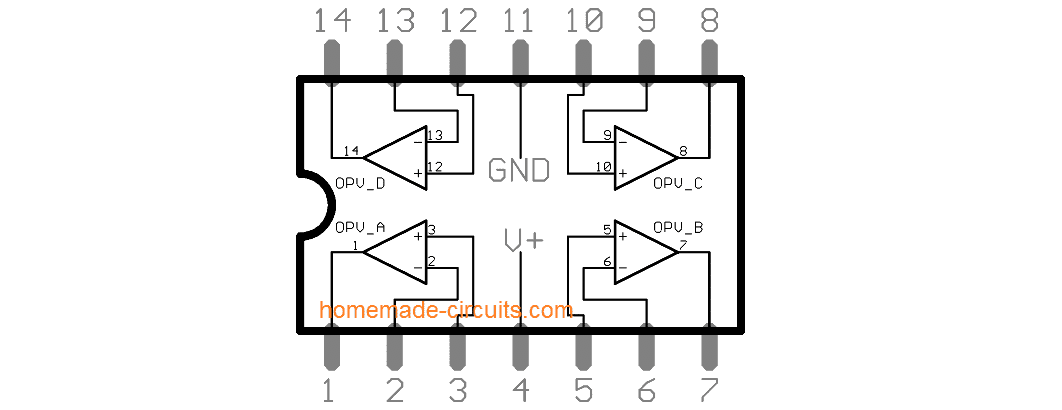

Postavitev IC CMOS

Pogled od zgoraj na na CMOS izdelava in postavitev je podan. Tu lahko jasno opazimo različne kovinske kontakte in difuzije N vrtin.

Postavitev IC CMOS

Tu gre torej za to Tehnike izdelave CMOS . Upoštevajmo ploščo velikosti 1 na kvadrat, razdeljeno na 400 žetonov s površino 50 mil x 50 mil. Za izdelavo tranzistorja je potrebno površino 50 mil2. Vsak IC torej vsebuje 2 tranzistorja, tako da sta na vsaki plošči vgrajeni 2 x 400 = 800 tranzistorjev. Če obdelamo 10 rezin v vsaki seriji, lahko hkrati izdelamo 8000 tranzistorjev. Katere različne komponente ste opazili na IC?